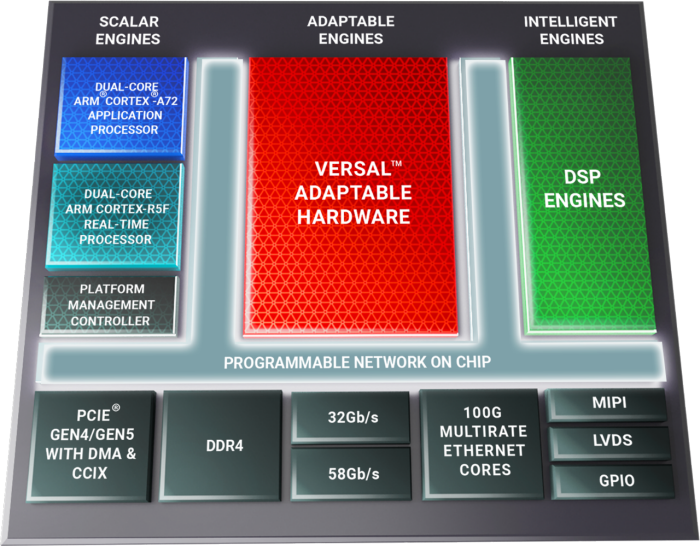

針對連接、內聯加速以及不同工作負載進行了優化

標量引擎

Versal® ACAP 中提供了三種標量處理器類型,可支持各種應用需求。應用處理單元非常適合操作係統支持的複雜應用,實時處理單元非常適合需要低時延、確定性以及實時控製的應用。一款單獨的平台管理控製器管理係統啟動、安全性與調試。

自適應引擎

可編程邏輯可實現為不斷變化的算法開發自定義計算模塊。Versal ACAP 中重新架構的邏輯可為每個 CLB 提供 4 倍的密度,從而可減少對高成本全局路由的需要。這些靈活應變的引擎加載了各種廣泛的內存元件,並與可編程 I/O 緊密耦合,允許用戶為任何應用創建強大的加速器。

智能引擎

增強的 DSP 引擎可為最新工作及數據類型提供支持,包括統一半精度浮點運算以及複雜的 18x18 工作。有了對 UltraScale+™ 設計的向後兼容性,用戶可不斷利用現有的庫和 IP 或更新他們的設計,來獲得這種新架構帶來的更高計算性能。

下一代 I/O

Versal Prime 係列將 PCIe® Gen4/Gen5 合規性、CCIX 支持、高性能 GPIO 以及支持各種以太網配置的多速率以太網 MAC 進行完美結合,可最大限度提高連接性和靈活性。此外,Versal Prime 係列器件還具有重新架構的低時延 32.75Gb/s 的收發器,而且某些器件還支持 58Gb/s 的 PAM4 收發器。

集成型 DDR 內存控製器

每款集成型 DDR 內存控製器不僅提供高達 34.1Gb/s 的帶寬,支持 DDR4 和 LPDDR4,而且還針對線性及隨機流量進行了優化。這些集成型控製器與片上可編程網絡相結合,無需在可編程邏輯中進行軟實現,從而可節省開發時間和邏輯資源。

可編程的片上網絡

可編程片上網絡 (NoC) 在 Versal ACAP 架構中的不同計算引擎與集成 IP 模塊之間提供了優化的多兆位互連,從而簡化了時序收斂並節省了邏輯資源。NoC 編譯器不僅提供優化的編程體驗,同時還允許用戶管理時延和 QoS,可確保關鍵數據路徑為優先級。

Versal Prime 係列支持高性能和高靈活性,可解決廣泛的特定行業問題。

存儲加速

隨著人工智能的出現以及現代應用所生成數據的激增,傳統計算已經成為數據中心越來越寶貴的資源。保存計算的一個解決方案是在存儲控製器和端點中添加加速器,以卸載主處理器的壓縮以及其它常見任務。Versal® Prime 係列將 PCIe® Gen4/Gen5 支持、強大的 Arm® 標量處理引擎、集成型內存控製器以及新一代可編程邏輯相結合,不僅可減少係統級瓶頸問題,而且還可提高效率。

數據中心網絡加速

FPGA 和 SoC 長期以來一直在加速數據中心應用中發揮著重要作用,它們可卸載係統中中央處理器的加密/解密以及虛擬交換等常見網絡功能,從而可保存計算周期。Versal ACAP 通過將 PCIe Gen4/Gen5 支持、新一代 SerDes 和多速率以太網 MAC 與強大的異構計算引擎相結合,進一步加速數據中心係統,以減輕網絡運算的負載,並通過額外的內聯處理來補充服務器中可用的計算。

5G xHaul

隨著 5G 的出現,對高帶寬連接的需求要求接入網絡,才能在適應支持 eCPRI 等新協議的同時,仍保持與現有標準的兼容。在 Versal Prime 係列中將靈活應變的引擎與行業領先的串行解串器和以太網技術相結合,不僅可為運營商提供處理 5G 吞吐量需求所需的處理能力,同時還可維護對原有標準的支持,並降低總體擁有成本。

無源光網

隨著無線服務競爭的加劇,有線寬帶提供商必須擴展其網絡並提供更高的帶寬服務,才能保持競爭力。Versal Prime 係列提供比現有 MPSoC 器件高 1 倍的可編程邏輯、強大的 Arm 標量處理引擎、更高的串行解串器密度、集成型以太網 IP 塊以及散熱優化封裝,可在不影響性能的情況下,實現低功耗的高效設計。

通信測試設備

伴隨最新通信標準的帶寬爆炸式增長,使測試設備廠商很難跟上市場需求的發展步伐。Versal Prime 係列现金网博e百 支持 58G 收發器和多速率以太網 MAC,可為有線通信測試人員提供高性能的數據處理和分析。可編程 NoC 和集成型內存控製器可為複雜的測試算法實現快速高效的數據移動。

Versal® Prime 係列功能概述

標量引擎功能

| VM1102 | VM1302 | VM1402 | VM1502 | VM1802 | VM2202 | VM2302 | VM2502 | VM2902 | |

|---|---|---|---|---|---|---|---|---|---|

| 應用處理單元 | 雙核 Arm® Cortex -A72、48KB/32KB L1 高速緩存支持奇偶校驗和 ECC,1MB L2 高速緩存支持 ECC | ||||||||

| 實時處理單元 | 雙核 Arm® Cortex -R5F、32KB/32KB L1 高速緩存以及支持 ECC 的 256KB TCM | ||||||||

| 存儲器 | 支持 ECC 的 256KB 片上內存 | ||||||||

| 連接功能 | 以太網 (x2)、USB 2.0 (x1)、UART (x2)、SPI (x2)、I2C (x2)、CAN-FD (x2) | ||||||||

智能引擎功能

| VM1102 | VM1302 | VM1402 | VM1502 | VM1802 | VM2202 | VM2302 | VM2502 | VM2902 | |

|---|---|---|---|---|---|---|---|---|---|

| DSP 引擎 | 464 | 832 | 1,696 | 1,312 | 1,968 | 1,312 | 1,904 |

3,984 | 2,672 |

靈活應變的引擎功能

| VM1102 | VM1302 | VM1402 | VM1502 | VM1802 | VM2202 | VM2302 | VM2502 | VM2902 | |

|---|---|---|---|---|---|---|---|---|---|

| 係統邏輯單元 (K) | 329 | 693 | 1,238 | 981 |

1,968 | 1,139 | 1,575 | 1,969 | 2,233 |

| LUT 數 | 150,272 | 316,928 | 565,760 | 448,512 |

899,840 | 520,704 | 719,872 | 900,224 | 1,020,928 |

基礎平台功能

| VM1102 | VM1302 | VM1402 | VM1502 | VM1802 | VM2202 | VM2302 | VM2502 | VM2902 | |

|---|---|---|---|---|---|---|---|---|---|

| NoC 主 / NoC 從端口 | 5 | 9 | 18 | 21 |

28 | 21 | 30 | 28 |

42 |

| DDR 內存控製器 | 1 | 2 | 4 | 3 |

4 | 3 | 3 |

4 |

3 |

| CCIX & PCIe® (帶有 DMA) (CPM) | - | 1 x Gen4x16、CCIX | 1 x Gen4x16、CCIX | 1 x Gen4x16、CCIX | 1 x Gen4x16、CCIX | 2 x Gen5x8, CCIX | - |

2 x Gen5x8, CCIX | - |

| PCIe | 1 x Gen4x8 | 2 x Gen4x8 | 2 x Gen4x8 | 4 x Gen4x8 | 4 x Gen4x8 | 4 x Gen5x4 | 2 x Gen5x4 | 2 x Gen5x4 | 2 x Gen5x4 |

| 100G Multirate Ethernet MAC | 1 | 2 | 2 | 4 | 4 | 2 | 6 | 2 | 6 |

| GTY 收發器 | 0 | 24 | 24 | 44 | 44 | 0 | 0 | 0 | 0 |

| GTYP 收發器 | 8 |

0 | 0 | 0 | 0 | 32 | 8 |

28 |

8 |

| GTM 收發器 | 0 |

0 |

0 |

0 |

0 |

0 | 40 | 20 | 40 |

技術文檔

搜索文檔

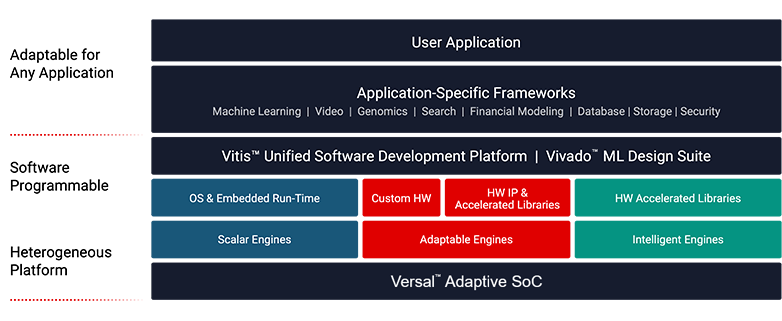

麵向所有真人百家乐游戏开户 的集成型軟硬件平台

Versal® ACAP 采用固有的軟件可編程芯片基礎架構,從零開始設計,以軟件為中心。增強型 Xilinx® Vivado® ML 版引入全新係統設計方法和開發環境,如流量分析儀、NoC 編譯器和數據流建模等。一個緊密結合的高速、統一調試環境可加速跨靈活應變的標量智能引擎的調試與跟蹤。

下載 Vivado ML 版 >

Xilinx Vitis™ 統一軟件平台提供了全麵的核開發套件,以及使用硬件加速技術的庫。該平台提供從雲端到邊緣的高效、便捷、統一的軟件環境。作為開源社區的重要成員,Vitis 統一軟件平台是完全免費和開源的。

下載 Vitis™ 統一軟件平台 >

Versal ACAP 評估套件

歡迎率先體驗 Versal ACAP 架構,從頭開始構建,實現原生的軟件可編程性。通過一係列工具、軟件、庫、IP、中間件和固件,ACAP 可通過業界標準設計流程實現各種定製化的加速計算解決方案。Versal Prime 係列 VMK180 評估套件擁有快速啟動設計所需的所有組件。

培訓課程

Xilinx 培訓和學習資源提供了實用的實踐技能和基礎知識,可助力真人百家乐游戏开户 在下一個開發項目中充分發揮生產力。

使用 Xilinx Versal ACAP 平台開啟設計

使用 Versal ACAP 進行設計:架構和方法

使用 Versal ACAP 進行設計:可編程片上網絡

使用 Versal ACAP 進行設計 - 電源和開發板設計