Versal HBM 係列

高速存儲器、安全數據和自適應計算的超級集成

Versal® HBM ACAP 融合了高速存儲器、安全連接和自適應計算,可消除內存受限、計算密集型工作負載(如機器學習、數據庫加速、新一代防火牆和高級網絡測試器)的處理與內存瓶頸。它是零基礎構建,可適應不斷發展的算法、協議和數據速率。觀看簡介視頻,了解更多詳情。

Versal HBM 係列集成了 HBM2e DRAM,與 DDR5 相比,存儲器帶寬1提高 8 倍、功耗降低 63%。Versal HBM 係列在經量產驗證的 Versal Premium ACAP 係列的基礎上構建,集成了廣泛的多太比特( multi-terabit )網絡連接、功耗優化型鏈接內核、112Gb/s PAM4 收發器,以靈活適應不斷演進的算法和新興協議。Versal HBM ACAP 在將收發器速度提高一倍的同時,可使用內建加密引擎為網絡基礎架構的每一層提供安全保護。有了可編程片上網絡 (NoC),高達 2.2Tb/s 的片上連接可緩解所有引擎之間的路由擁塞。此外,Versal HBM ACAP 還可提供比上一代 HBM 解決方案高 1 倍的邏輯密度,從而可為不斷演進的算法和協議最大限度提高性能。

1. 基於帶有四個 DDR5-6400 組件的典型係統實現方案

主要特性

集成的 HBM2e

該係列集成了 HBM2e 技術,可提供 820GB/s 存儲器帶寬和 32GB 容量,為計算密集型應用降低功耗、時延、外形尺寸。與商用內存解決方案 DDR5 相比,Versal HBM ACAP 通過將堆疊內存放置在緊鄰計算結構的位置,使存儲器帶寬提高 8 倍、功耗降低 63%。集成的 HBM 可通過可編程 NoC,從全球任何地方訪問設備。通過集成的內存控製器和增強的硬化交換機功能,可從任何端口訪問任何內存位置。

可擴展的串行帶寬

Versal HBM 係列由 58G/112Gb/s PAM4 和 32Gb/s NRZ 收發器組成,具有高度可擴展的收發器,可提供高達 5.6Tb/s 的串行 I/O 帶寬。112G PAM4 收發器有助於行業推出 800G 及單信道 100G 容量的基礎架構。 對於 400G 的提升與部署,58G PAM4 收發器可針對最大帶寬密度實現最新一代接口。 對於電源優化的主流 100G 接口,32Gb/s NRZ 收發器最為理想。可擴展的串行帶寬

高性能連接是新一代網絡及雲基礎架構的基礎。

Versal HBM 係列可提供前所未有的電源優化硬 IP 集成,相當於 14 個 Virtex® UltraScale+™ FPGA 的邏輯密度。Versal HBM ACAP 具有高速以太網、Interlaken 以及支持 DMA 的 PCIe®Gen5,可提供幾太字節的連接,為一係列協議和數據速率帶來高度的靈活性。Versal HBM ACAP 具有高速以太網、Interlaken,以及內置 DMA 的 PCIe® Gen5,為各種協議和數據速率提供了多太比特( multi-terabit )網絡連接。線速高速加密引擎可以完全保護網絡流量。

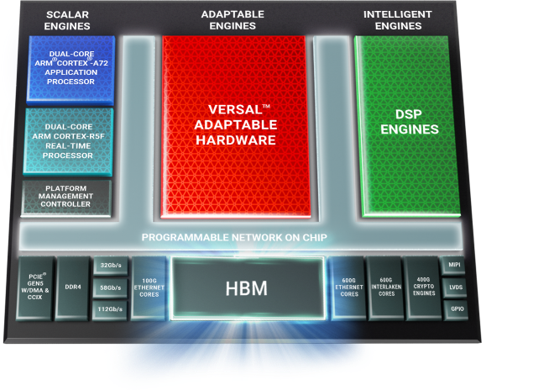

自適應引擎

靈活應變的引擎加載了各種各樣的片上內存元件,與可編程 I/O 緊密耦合,可提供海量並行處理和定製化功能,這對於許多具有大型數據集的計算密集型工作負載而言至關重要。作為上一代技術的增強版本,DSP 引擎向後兼容於 UltraScale+ FPGA 和 SoC 設計。

智能引擎

DSP 引擎支持多種操作係統和數據類型,包括單精度和半精度浮點以及複雜的 18x18 運算。因此,用戶獲得最大的計算性能,既可利用現有的庫,也可更新其設計。您可利用現有的庫或更新設計以獲得最大的計算性能。

標量引擎

三種標量處理器可支持不同的應用需求。應用處理單元非常適合操作係統支持的複雜應用,實時處理單元非常適合時延敏感型應用。單獨的平台管理控製器管理係統啟動、安全性、功耗管理和調試。

了解更多詳情

了解更多有關 Xilinx 存儲器解決方案的信息

了解更多有關 Versal HBM 係列的詳情

加入 Versal ACAP 通知列表,即可第一時間獲取最新的新聞和信息。

人工智能和機器學習 (AI/ML) 發展迅速;複雜的算法需要處理大量的數據,因此需要極高的內存帶寬。

機器學習加速

在傳統計算架構中,當多個 CPU 內核同時工作時,由於數據從外部內存移動的速度不足而且最終會達到極限,因此係統會停止運行。在傳統計算架構中,當多個 CPU 內核同時工作時,由於數據從外部內存移動的速度不足而且最終會達到極限,因此係統會停止運行。相比之下,Versal® HBM 係列通過靈活應變的引擎和智能引擎提供海量並行處理能力,並通過集成型 HBM 提供極高的存儲器帶寬。 因此,Versal HBM 係列能夠為許多 AI/ML 處理(如餘弦相似度和 Louvain 模塊化)實現更快速度的精確數據洞察。通過一係列廣泛的 Vitis™ 統一軟件平台的性能優化庫,基於 Versal HBM ACAP 的解決方案可以為快速發展的數據中心及雲計算人工智能提供更高的 AI/ML 性能與效率。

計算預處理與緩衝

預處理數據對於從固定函數計算器件獲得最佳結果至關重要。真實 ML 模型的數據集大小很容易超過太字節。因此,目標加速器需要大型數據預處理框架來高效處理這些數據集。使用靈活應變的引擎和 820GB/s 的 HBM 帶寬,Versal HBM ACAP 可刪除不需要的數據,轉換選定的數據,並增強數據,從而可為目標加速器創建強大的預測輸入。Versal HBM 係列配備高速 112G PAM4 收發器,能夠以低時延最大限度提高吞吐量和係統性能。

新一代防火牆

網絡運營商希望實現不間斷的智能管理並提供穩健的網絡,以保護數據並避免對企業網絡的攻擊。

Versal HBM 係列可實現無與倫比的可擴展性,有助於實現從物理層和數據鏈路層到 VPN,再到傳輸層安全級別的多層網絡安全性,從而可通過定製策略及控製實現數以千萬計的同時會話。此外,多個 400G 集成型高速加密 (HSC) 引擎允許係統在不影響性能的情況下,保持行速率吞吐量和低時延。使用 32G HBM,新一代防火牆可以管理多個查找表,無需訪問外部內存來緩衝網絡流量並對其進行重新排序。112G PAM4 收發器可實現對最新可擴展光學標準和協議的支持,帶來新一代防火牆所需的更高吞吐量。靈活應變的引擎有助於 ML 算法針對新興威脅為安全架構實現現代化。

應用性能測試設備

隨著數據中心、雲計算和人工智能網絡開始為 800G 光網連接做準備,許多數據中心網絡和雲計算服務提供商需要利用尖端測試設備,才能為計算密集型應用確保互操作性和穩健的網絡基礎架構。

Versal HBM 器件中的 112G PAM4 收發器是最重要的構建模塊之一,可幫助數據中心網絡及雲計算服務提供商構建能夠適應新興協議和光學互操作性的網絡。專用信道化多速率以太網內核提供可單獨訪問的 HSC、MAC、PCS 和 FEC 模塊以及 32G HBM 和可編程 NoC,可為 L4-L7 測試設備的海量流量緩衝、高效數據移動、智能數據流控製、跟蹤與報告實現最複雜的測試邏輯。

Versal® HBM 係列现金网博e百 表

內存特性

| VH1522 | VH1542 | VH1582 | VH1742 | VH1782 | |

|---|---|---|---|---|---|

| HBM DRAM (GB) | 8 | 16 | 32 | 16 | 32 |

| 總體模塊 RAM (Mb) | 89 | 89 | 89 | 132 | 132 |

| UltraRAM (Mb) | 366 | 366 | 366 | 541 | 541 |

| 總 PL 存儲 (Mb) | 509 | 509 | 509 | 752 | 752 |

智能引擎功能

| VH1522 | VH1542 | VH1582 | VH1742 | VH1782 | |

|---|---|---|---|---|---|

| DSP 引擎 | 7,392 | 7,392 | 7,392 | 10,848 | 10,848 |

靈活應變的引擎功能

| VH1522 | VH1542 | VH1582 | VH1742 | VH1782 | |

|---|---|---|---|---|---|

| 係統邏輯單元 (K) | 3,837 | 3,837 | 3,837 | 5,631 | 5,631 |

| LUT (M) | 1.75 | 1.75 | 1.75 | 2.57 | 2.57 |

標量引擎功能

| VH1522 | VH1542 | VH1582 | VH1742 | VH1782 | |

|---|---|---|---|---|---|

| 應用處理單元 | 雙核 Arm® Cortex -A72、48KB/32KB L1 高速緩存支持奇偶校驗和 ECC,1MB L2 高速緩存支持 ECC | ||||

| 實時處理單元 | 雙核 Arm® Cortex -R5F、32KB/32KB L1 高速緩存以及支持 ECC 的 256KB TCM | ||||

| 存儲器 | 支持 ECC 的 256KB 片上內存 | ||||

| 連接功能 | Ethernet (x2); UART (x2); CAN-FD (x2); USB 2.0 (x1); SPI (x2); I2C (x2) | ||||

平台功能

| VH1522 | VH1542 | VH1582 | VH1742 | VH1782 | |

|---|---|---|---|---|---|

| GTYP 收發器 (32.75Gb/s) | 68 | 68 | 68 | 68 | 68 |

| GTM 收發器 (56G (112G)) | 20 (10) | 20 (10) | 20 (10) | 60 (30) | 60 (30) |

| CCIX & PCIe® (帶有 DMA) (CPM) | 2 | 2 | 2 | 2 | 2 |

| PCIe | 8 | 8 | 8 | 8 | 8 |

| 400G 高速加密引擎 | 2 | 2 | 2 | 3 | 3 |

| 100G Multirate Ethernet MAC | 4 | 4 | 4 | 6 | 6 |

| 600G Ethernet MAC | 1 | 1 | 1 | 3 | 3 |

| 600G Interlaken | 0 | 0 | 0 | 1 | 1 |

技術文檔

早期訪問計劃

Versal® HBM 係列目前處於早期訪問階段。聯係本地銷售代表,申請加入搶先體驗計劃,或訪問聯係銷售頁麵。歡迎利用以下資源進一步了解 Versal ACAP 架構的設計工具和設計方法。

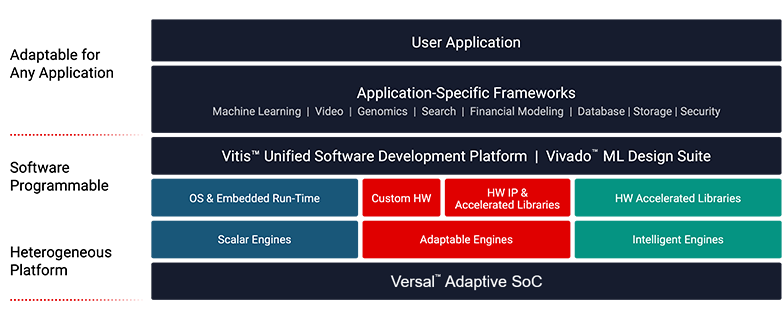

麵向所有真人百家乐游戏开户 的集成型軟硬件平台

Versal ACAP 采用固有的軟件可編程芯片基礎架構,其設計自始至終都是以軟件為導向的。增強型 Xilinx® Vivado® ML 版引入全新係統設計方法和開發環境,如流量分析儀、NoC 編譯器和數據流建模等。一個緊密結合的高速、統一調試環境可加速跨靈活應變的標量智能引擎的調試與跟蹤。

下載 Vivado ML 版 >

Xilinx Vitis™ 統一軟件平台提供了全麵的核開發套件,以及使用硬件加速技術的庫。該平台提供從雲端到邊緣的高效、便捷、統一的軟件環境。作為開源社區中引以為傲的一員,Vitis 統一軟件平台不僅免費,而且還提供一係列性能優化的廣泛開源庫,這些庫可提供開創性加速,對於現有應用而言,代碼修改很少,甚至無需修改。

下載 Vitis 統一軟件平台 >

使用 Versal Premium VPK120 評估套件開始開發

麵向 Versal HBM 器件的設計人員現在可使用 Versal Premium VPK120 評估套件啟動設計。Versal HBM 器件基於與 Versal Premium 係列相同的架構,具有各種通用架構模塊,如標量引擎(Arm® 處理子係統)、靈活應變引擎(可編程邏輯)、DSP 引擎、可編程片上網絡 (NoC) 和連接塊(包括 PCIe®)、400G 高速加密引擎、600G 以太網 MAC、100G 多速率以太網 MAC、600G Interlaken 內核以及 DDR4 控製器等。評估套件擁有啟動設計所需的一切,包括執行係統測試、評估關鍵接口以及采用 ACAP 設計方法的功能。

現在可搶先體驗 Versal Premium VPK120 評估套件。聯係本地銷售代表,申請加入搶先體驗計劃,或訪問聯係銷售頁麵。

培訓課程

Xilinx 培訓和學習資源提供了實用的實踐技能和基礎知識,可助力真人百家乐游戏开户 在下一個開發項目中充分發揮生產力。

Xilinx Versal® ACAP 平台快速上手

使用 Versal ACAP 進行設計 - 電源和開發板設計

使用 Versal ACAP 進行設計:架構和方法

使用 Versal ACAP 進行設計:可編程片上網絡