Versal AI Core 係列

Versal AI Core 係列憑借集成型 AI 引擎實現了突破性 AI 推斷和無線加速,與當今的服務器級 CPU 相比,可提供超過 100 倍的計算性能

擁有现金网博e百 組合的最高計算能力,可實現最大的 AI 和工作負載加速

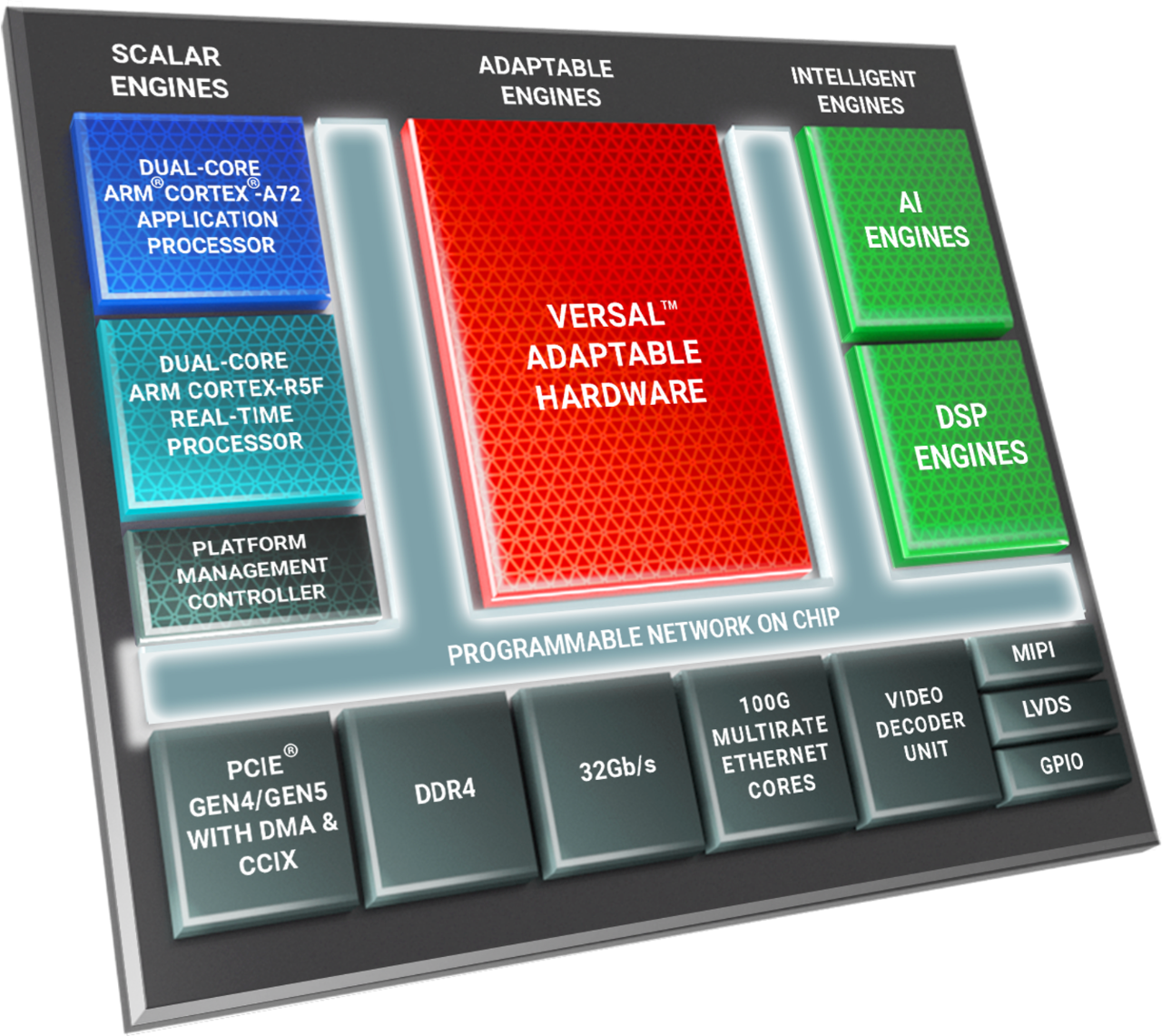

標量引擎

Versal® ACAP 中提供了三種標量處理器類型,可支持各種應用需求。應用處理單元適合 OS 支持的複雜應用,而實時處理單元則完美適合需要低延遲、確定性和實時控製的應用。單獨的平台管理控製器管理係統引導、安全性和調試。

自適應引擎

可編程邏輯可為不斷變化的算法開發自定義計算模塊。Versal ACAP 中重新排列的邏輯使每個 CLB 的密度提高 4 倍,從而減少了對昂貴全局路由的需求。自適應引擎裝載了各類存儲元件,並與可編程 I/O 緊密結合,使用戶可為任意應用創建強大的加速器。

智能引擎

AI 引擎為基於矢量的算法提供高達 5 倍的計算密度。AI 引擎針對實時 DSP 和 AI / ML 計算進行了優化,可提供確定性的性能。

增強的 DSP 引擎為新操作和數據類型提供支持,包括單精度和半精度浮點以及複雜的 18x18 操作。

下一代 I/O

Versal AI Core 係列結合了PCIe® Gen4/Gen5 合規性、CCIX 支持、高性能 GPIO 和支持各種以太網配置的多速率以太網 MAC,以最大程度地提升連接功能能和靈活性。此外,Versal AI Core 係列器件還具有重配置的低延遲 32.75Gb/s 收發器。

視頻解碼器單元

功率優化的強化視頻解碼器單元 (VDU) 包括多個視頻解碼器引擎 (VDE),支持 H.264 和 H.265,從每個引擎單個 4Kp60 流到多達 32 個 720p15 流。VDU 是許多圖像處理應用的理想選擇,其中多個視頻輸入為中央集線器提供解碼和執行高級 ML 算法。

可編程的片上網絡

可編程片上網絡 (NoC) 在 Versal ACAP 架構中的不同計算引擎與集成 IP 模塊之間提供了優化的多兆位互連,從而簡化了時序收斂並節省了邏輯資源。NoC 編譯器提供了簡化的編程體驗,同時允許用戶管理延遲和 QoS,從而確保對關鍵數據路徑進行優先級排序。

Versal AI Core 係列器件針對計算密集型應用進行了優化,特別是數字信號處理、人工智能和機器學習

5G 無線電與波束形成

波束成形導致巨大的信號處理需求,這些需求需要實時處理。自適應引擎處理狀態控製和數據格式化時,AI 引擎和 DSP 引擎正在處理定點和浮點信號處理工作負載,以實現高性能並行處理。

數據中心計算

隨著卷積神經網絡的不斷發展,隻有通過 Versal® AI Core 係列器件才可解決不斷增長的計算密度要求,Versal AI Core 係列器件的 AI 引擎經過優化,可有效地交付計算密度,既節省成本又節省能源。

麵向智能城市的視頻處理

Versal AI Core 係列器件支持在智能城市邊緣部署大量新的視頻處理應用,其中 AI 引擎驅動實時車牌、麵部識別或對象分類、用於視頻轉碼的視頻解碼器單元和用於視頻縮放、壓縮和自定義的自適應引擎 。

醫療圖像處理

Versal AI Core 係列可加速並行波束形成和實時圖像處理,以創建更高質量的圖像和基於機器的圖像分析,從而使醫生和放射科醫生能夠更快、更準確地進行診斷。

雷達處理

將功能強大的、基於矢量的 DSP 引擎與較小尺寸的 AI 引擎相結合,可實現先進的雷達,例如有源電子掃描陣列。AI Core 係列器件在單個封裝中提供每秒兆位的天線帶寬。

無線測試設備

實時 DSP 被廣泛用於無線通信測試設備中。Versal AI 引擎架構完美適合處理所有類型的協議實現,包括從數字前端到波束成形和基帶的 5G。

Versal® AI Core 係列功能簡介

標量引擎功能

| VC1352 | VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|---|

| 應用處理單元 | 雙核 Arm® Cortex -A72、48KB/32KB L1 高速緩存支持奇偶校驗和 ECC,1MB L2 高速緩存支持 ECC | ||||||

| 實時處理單元 | 雙核 Arm® Cortex -R5F、32KB/32KB L1 高速緩存以及支持 ECC 的 256KB TCM | ||||||

| 存儲器 | 支持 ECC 的 256KB 片上內存 | ||||||

| 連接功能 | 以太網 (x2)、USB 2.0 (x1)、UART (x2)、SPI (x2)、I2C (x2)、CAN-FD (x2) | ||||||

智能引擎功能

| VC1352 | VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|---|

| AI 引擎 | 128 | 248 | 304 | 300 | 400 | 0 | 0 |

| AI 引擎-ML | 0 | 0 | 0 | 0 | 0 | 152 | 304 |

| DSP 引擎 | 928 | 1,312 | 1,312 | 1,600 | 1,968 | 984 | 1,312 |

靈活應變的引擎功能

| VC1352 | VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|---|

| 係統邏輯單元 (K) | 540 | 797 | 981 | 1,586 | 1,968 | 820 | 1,139 |

| LUT (K) | 247 | 372 | 449 | 725 | 900 | 375 | 521 |

平台功能

| VC1352 | VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|---|

| NoC 主 / NoC 從端口 | 10 | 21 | 21 |

28 | 28 | 21 | 21 |

| DDR 內存控製器 | 2 | 3 | 3 |

4 | 4 | 3 | 3 |

| CCIX & PCIe® (帶有 DMA) (CPM) | - | 1 x Gen4x16, CCIX |

1 x Gen4x16, CCIX |

1 x Gen4x16, CCIX |

1 x Gen4x16, CCIX |

2 x Gen5x8, CCIX |

2 x Gen5x8, CCIX |

| PCIe Express® | 1 x Gen4x8 | 4 x Gen4x8 | 4 x Gen4x8 | 4 x Gen4x8 | 4 x Gen4x8 | 4 x Gen5x4 | 4 x Gen5x4 |

| 100G Multirate Ethernet MAC | 1 | 3 | 4 | 4 | 4 | 2 | 2 |

| 視頻解碼器引擎 (VDE) | - | - | - | - | - | 2 | 4 |

| GTY 收發器 | 0 | 32 | 44 | 44 | 44 | 0 | 0 |

| GTYP 收發器 | 8 | 0 | 0 | 0 | 0 | 32 | 32 |

技術文檔

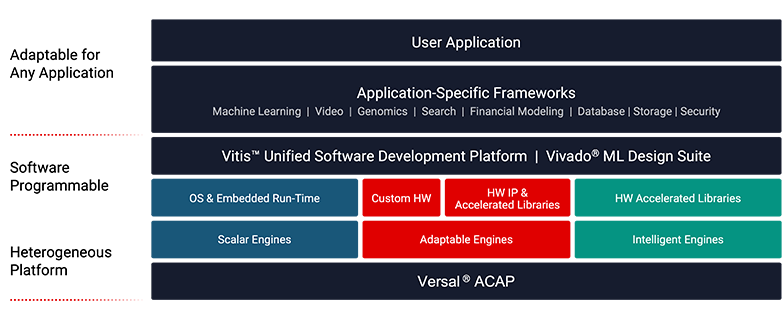

麵向所有真人百家乐游戏开户 的集成型軟硬件平台

Versal® ACAP 采用固有的軟件可編程芯片基礎架構,從零開始設計,以軟件為中心。增強型 Xilinx® Vivado® ML 版引入全新係統設計方法和開發環境,如流量分析儀、NoC 編譯器和數據流建模等。一個緊密結合的高速、統一調試環境可加速跨靈活應變的標量智能引擎的調試與跟蹤。

下載 Vivado ML 版 >

Xilinx Vitis™ 統一軟件平台提供了全麵的核開發套件,以及使用硬件加速技術的庫。該平台提供從雲端到邊緣的高效、便捷、統一的軟件環境。Vitis 統一軟件平台是開源社區引以為傲的一份子,完全免費、開源。

下載 Vitis 統一軟件平台 >

Versal ACAP 評估套件

歡迎率先體驗 Versal ACAP 架構,從零開始構建,實現原生的軟件可編程性。通過一係列工具、軟件、庫、IP、中間件和構架,ACAP 可通過業界標準設計流程實現各種定製化的加速計算解決方案。Versal AI Core 係列 VCK190 評估套件提供快速啟動設計所需的一切。

培訓課程

Xilinx 培訓和學習資源提供了實用的實踐技能和基礎知識,可助力真人百家乐游戏开户 在下一個開發項目中充分發揮生產力。

使用 Xilinx Versal ACAP 平台開啟設計

使用 Versal ACAP 進行設計:架構和方法

使用 Versal ACAP 進行設計:可編程片上網絡

使用 Versal ACAP 進行設計 - 電源和開發板設計

使用 Versal AI 引擎進行設計 1 :架構與設計流程

使用 Versal AI 引擎進行設計 2:使用 AI 引擎內核進行圖形編程

使用 Versal AI Engine 3 進行設計 - 內核編程和優化