- 設計工具

- MicroBlaze Processor

AMD MicroBlaze™ 處理器

靈活高效的軟處理器

AMD MicroBlaze™ 處理器基於高效的 RISC Harvard 架構,提供一係列可定製、易於集成的 32/64 位微處理器配置。MicroBlaze 處理器提供高度的靈活性,允許對外設、內存和接口特性進行廣泛的定製。憑借其靈活應變性,MicroBlaze 處理器經過驗證,可為多個領域的各種應用帶來巨大的優勢,其中包括工業、醫療、汽車、消費類现金网博e百 以及通信市場等。

MicroBlaze 處理器經過試用、測試,值得信賴,其巨大的吸引力跨越幾代现金网博e百 從未凋零。多年來,它已在眾多應用中找到了自己的發展之路。其經久不衰的設計和高度可靠的性能讓客戶心生強烈的歸屬感,他們反複選擇 MicroBlaze 處理器為其始終如一的可靠性以及有目共睹的成功保駕護航。

開發人員可將 MicroBlaze 處理器對準由 Vivado™ 設計套件提供支持的任何 AMD 自適應 SoC 或 FPGA 器件,無需額外的費用。此外,它也可作為原有集成設計軟件 (IDS) 嵌入式版本的一部分提供,滿足較早 FPGA 现金网博e百 係列的需求,如 Spartan™ 6 FPGA。

| 主要功能 |

|---|

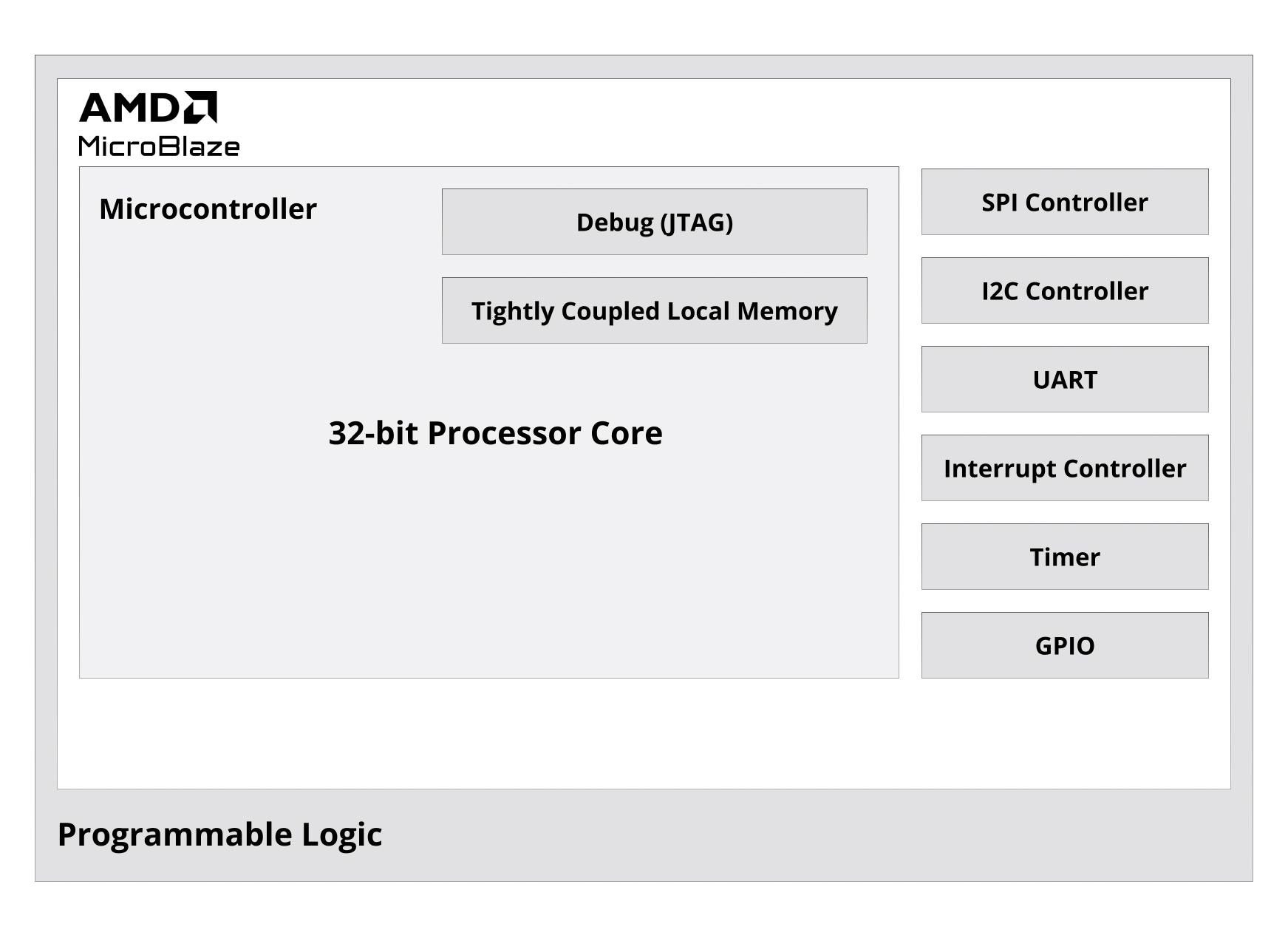

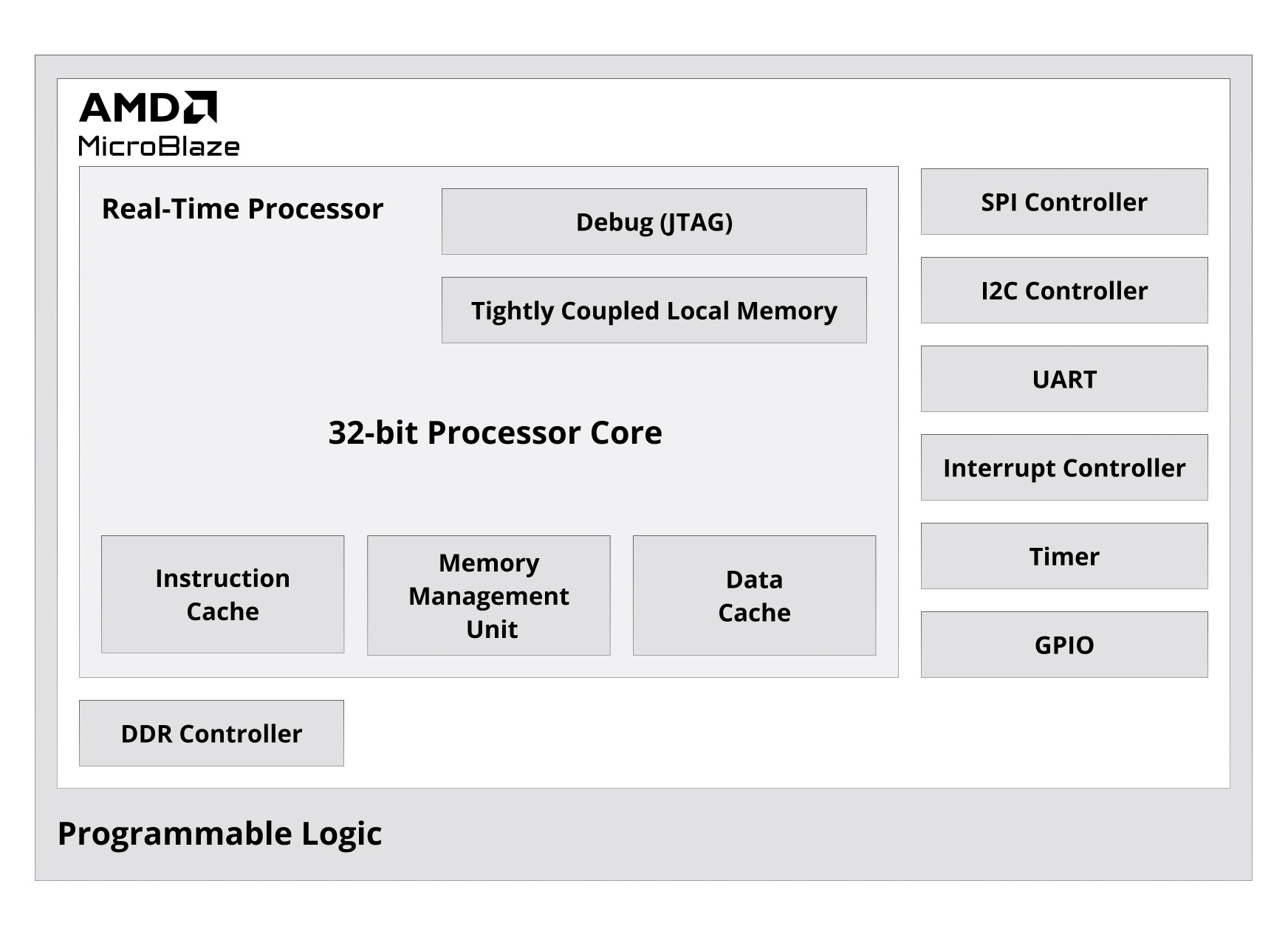

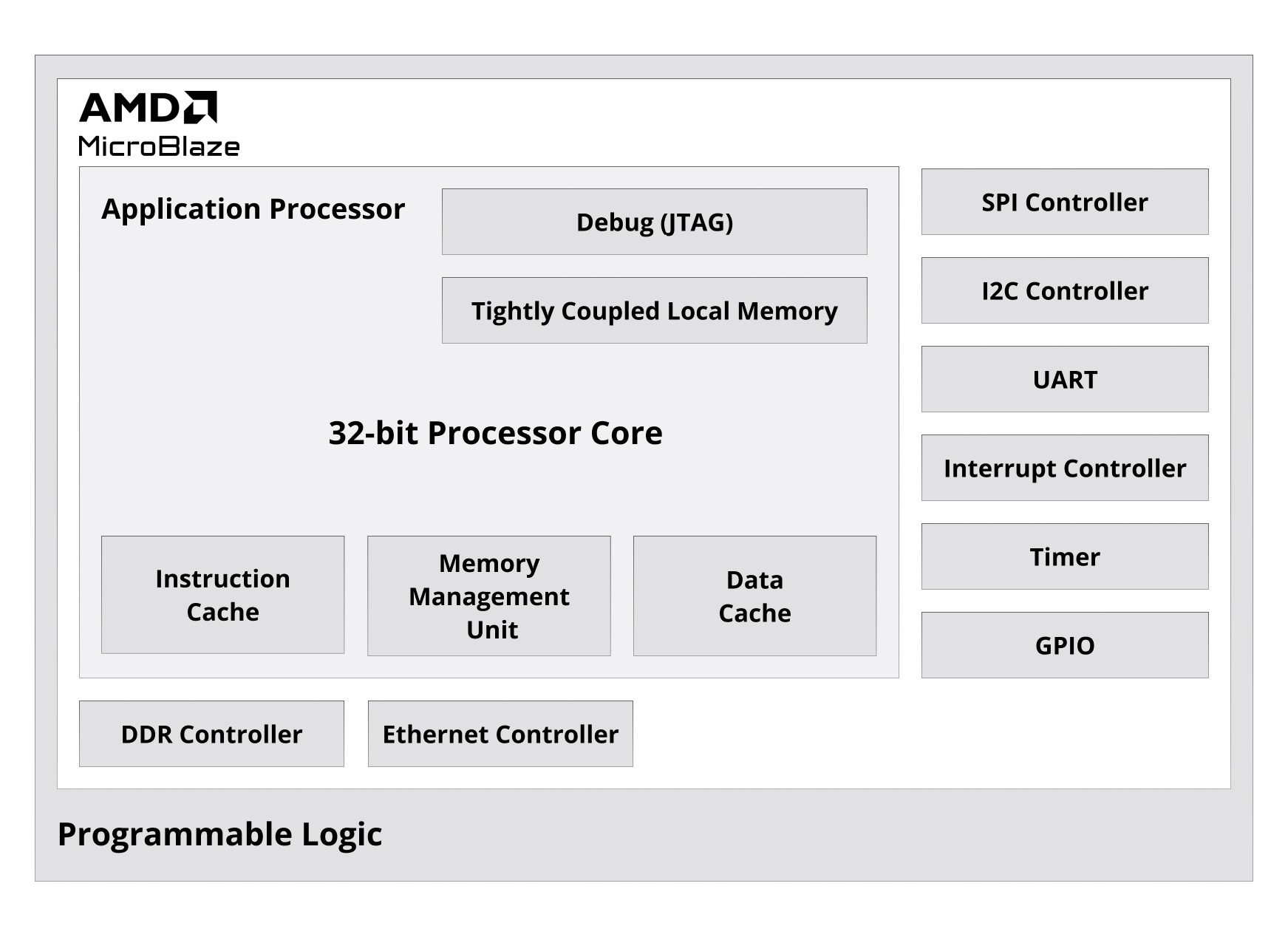

三種不同的配置:

高級特性:

高度的設計靈活性:

|

發現 AMD MicroBlaze™ V 處理器的潛能。這款處理器帶來了 RISC-V 開源優勢、便捷的硬件遷移、設計可移植性以及全麵的行業支持生態係統,不僅可優化設計,而且還可提供最佳的效率和安全特性。

主要拖放外設

| 一般用途 | I/O | 視頻 | 存儲器 | 網絡 |

|---|---|---|---|---|

|

|

|

|

|

示例設計配置

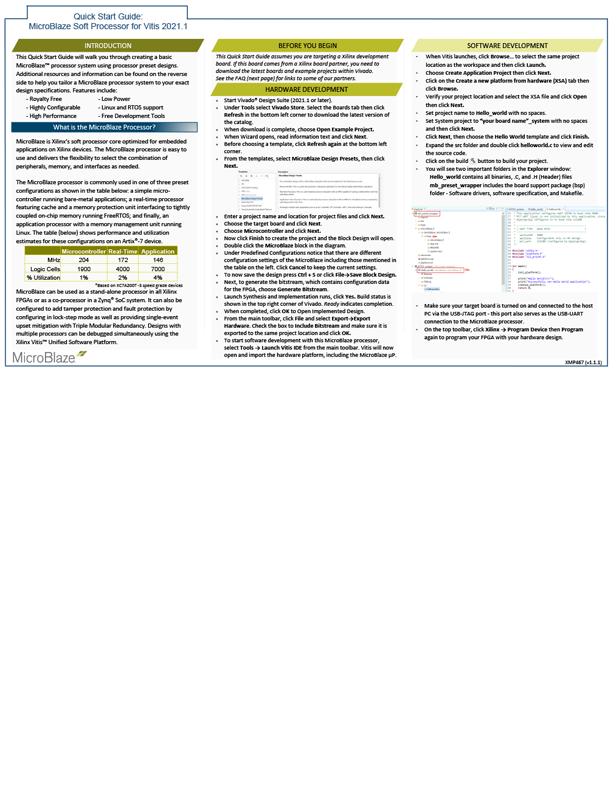

MicroBlaze™ 處理器性能指標:基於 Vivado™ Design Suite 2023.2

| 器件 | 微處理器 (1.09 DMIPs/MHz) |

實時處理器 (1.38 DMIPs/MHz) |

應用處理器 (1.38 DMIPs/MHz) |

|||

|---|---|---|---|---|---|---|

| Fmax | DMIPS | Fmax | DMIPS | Fmax | DMIPS | |

| 成本優化器件係列 | ||||||

| Spartan™ 7 (-2) FPGA | 186 | 203 | 152 | 210 | 132 | 182 |

| Artix™ 7 (-3) FPGA | 203 | 221 | 181 | 250 | 140 | 193 |

| Zynq™ 7000S (-2) SoC | 186 | 203 | 155 | 214 | 128 | 177 |

| Zynq 7000 (-3) SoC | 211 | 230 | 171 | 236 | 147 | 203 |

| FPGA、3D IC、MPSoC 和自適應 SoC | ||||||

| Kintex™ 7 (-3) FPGA | 295 | 322 | 243 | 335 | 204 | 282 |

| Virtex™ 7 (-3) FPGA | 299 | 326 | 252 | 348 | 202 | 279 |

| Kintex UltraScale™ (-3) FPGA | 392 | 427 | 291 | 402 | 244 | 337 |

| Virtex UltraScale (-3) FPGA | 384 | 419 | 283 | 391 | 243 | 335 |

| Kintex UltraScale+™ (-3) FPGA | 519 | 566 | 390 | 538 | 343 | 473 |

| Virtex UltraScale+ (-3) FPGA | 517 | 564 | 377 | 520 | 338 | 466 |

| Artix UltraScale+ (-2) FPGA | 482 | 525 | 358 | 494 | 300 | 414 |

| Zynq UltraScale+ MPSoC (-3) | 518 | 565 | 365 | 504 | 334 | 461 |

| Versal™ AI Core 係列 (-3HP) | 437 | 476 | 361 | 498 | 310 | 428 |

基於 2023 年 11 月的 AMD 內部測試,使用 Dhrystone 基準 V2.1 測試具有預定義預設和允許的編譯器選項的 AMD MicroBlaze 處理器,並使用 AMD Vivado 2023.2 IDE 中提供的 GNU 工具鏈。實際結果會有所不同。 (IP-001)