## Partial Reconfiguration Bitstream Monitor v1.0

LogiCORE IP Product Guide

Vivado Design Suite

PG304 (v1.0) December 5, 2018

## Table of Contents

| Chapter 1: IP Facts                                                                                                                                                                                                                        |                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Features                                                                                                                                                                                                                                   | 4                                                                                |

| IP Facts                                                                                                                                                                                                                                   | 4                                                                                |

| Chapter 2: Overview                                                                                                                                                                                                                        | 6                                                                                |

| Feature Summary                                                                                                                                                                                                                            |                                                                                  |

| Unsupported Features                                                                                                                                                                                                                       |                                                                                  |

| Licensing and Ordering                                                                                                                                                                                                                     |                                                                                  |

| Chapter 3: Product Specification                                                                                                                                                                                                           | 9                                                                                |

| Overview                                                                                                                                                                                                                                   |                                                                                  |

| Performance                                                                                                                                                                                                                                |                                                                                  |

| Resource Use                                                                                                                                                                                                                               |                                                                                  |

| Port Descriptions                                                                                                                                                                                                                          |                                                                                  |

| Register Space                                                                                                                                                                                                                             |                                                                                  |

|                                                                                                                                                                                                                                            |                                                                                  |

|                                                                                                                                                                                                                                            |                                                                                  |

| Chapter 4: Designing with the Core                                                                                                                                                                                                         |                                                                                  |

| USR ACCESS Primitive                                                                                                                                                                                                                       |                                                                                  |

| USR_ACCESS Primitive<br>Bitstream Growth                                                                                                                                                                                                   |                                                                                  |

| USR ACCESS Primitive                                                                                                                                                                                                                       |                                                                                  |

| USR_ACCESS Primitive<br>Bitstream Growth<br>Clocking                                                                                                                                                                                       |                                                                                  |

| USR_ACCESS Primitive<br>Bitstream Growth<br>Clocking<br>Chapter 5: Design Flow Steps                                                                                                                                                       | 23<br>23<br>23<br>23<br>23<br>25                                                 |

| USR_ACCESS Primitive<br>Bitstream Growth<br>Clocking<br><b>Chapter 5: Design Flow Steps</b><br>Customizing and Generating the Core                                                                                                         | 23<br>23<br>23<br>23<br>23<br>23<br>25                                           |

| USR_ACCESS Primitive<br>Bitstream Growth<br>Clocking<br><b>Chapter 5: Design Flow Steps</b><br>Customizing and Generating the Core<br>Constraining the Core                                                                                | 23<br>23<br>23<br>23<br>23<br>25<br>25<br>32                                     |

| USR_ACCESS Primitive<br>Bitstream Growth<br>Clocking<br><b>Chapter 5: Design Flow Steps</b><br>Customizing and Generating the Core<br>Constraining the Core<br>Simulation                                                                  | 23<br>23<br>23<br>23<br>23<br>23<br>25<br>25<br>32<br>33                         |

| USR_ACCESS Primitive<br>Bitstream Growth<br>Clocking<br><b>Chapter 5: Design Flow Steps</b><br>Customizing and Generating the Core<br>Constraining the Core<br>Simulation<br>Synthesis and Implementation                                  | 23<br>23<br>23<br>23<br>23<br>25<br>25<br>32<br>33<br>33                         |

| USR_ACCESS Primitive<br>Bitstream Growth<br>Clocking<br><b>Chapter 5: Design Flow Steps</b><br>Customizing and Generating the Core<br>Constraining the Core<br>Simulation                                                                  | 23<br>23<br>23<br>23<br>23<br>25<br>25<br>32<br>33<br>33                         |

| USR_ACCESS Primitive<br>Bitstream Growth<br>Clocking<br><b>Chapter 5: Design Flow Steps</b><br>Customizing and Generating the Core<br>Constraining the Core<br>Simulation<br>Synthesis and Implementation                                  | 23<br>23<br>23<br>23<br>23<br>25<br>25<br>32<br>32<br>33<br>33<br>33<br>33       |

| USR_ACCESS Primitive<br>Bitstream Growth<br>Clocking<br><b>Chapter 5: Design Flow Steps</b><br>Customizing and Generating the Core<br>Constraining the Core<br>Simulation<br>Synthesis and Implementation<br>Partial Bitstream Preparation | 23<br>23<br>23<br>23<br>25<br>32<br>32<br>33<br>33<br>33<br>33<br>33<br>33<br>33 |

| Debug Tools                                        | 38 |

|----------------------------------------------------|----|

| Appendix C: Additional Resources and Legal Notices |    |

| Xilinx Resources                                   |    |

| Documentation Navigator and Design Hubs            |    |

| References                                         |    |

| Training Resources                                 |    |

| Revision History                                   |    |

| Please Read: Important Legal Notices               | 42 |

|                                                    |    |

## Chapter 1

## **IP** Facts

The Xilinx<sup>®</sup> Partial Reconfiguration Bitstream Monitor can be used to identify partial bitstreams as they flow through the design. This information can be used for debugging or to help manage system applications such as blocking bitstream loads.

## Features

- ICAP, AXI4MM (partial support), AXI4-Lite and Generic datapaths supported

- Partial Bitstreams can be traced in the Configuration Engine

- Live and buffered status

- Optional Signal based or AXI4-Lite control

- Optional AXI4-Lite status (signal status is always available)

## **IP Facts**

| LogiCORE IP Facts Table                |                                       |  |

|----------------------------------------|---------------------------------------|--|

| Core Specifics                         |                                       |  |

| Supported Device Family <sup>(1)</sup> | UltraScale+™, UltraScale™, 7 series   |  |

| Supported User Interfaces              | AXI4-Lite                             |  |

| Resources                              | Performance and Resource Use web page |  |

|                                        | Provided with Core                    |  |

| Design Files                           | Encrypted RTL                         |  |

| Example Design                         | Not Provided                          |  |

| Test Bench                             | Not Provided                          |  |

| Constraints File                       | XDC                                   |  |

| Simulation Model                       | Source HDL                            |  |

| Supported S/W Driver <sup>2</sup>      | None                                  |  |

|                                        | Tested Design Flows <sup>3</sup>      |  |

| Design Entry                           |                                       |  |

|                                        |                                       |  |

| LogiCORE IP Facts Table                                        |                                                                             |  |

|----------------------------------------------------------------|-----------------------------------------------------------------------------|--|

| Simulation                                                     | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |

| Synthesis                                                      | Vivado Synthesis                                                            |  |

| Support                                                        |                                                                             |  |

| Provided by Xilinx <sup>®</sup> at the Xilinx Support web page |                                                                             |  |

#### Notes:

- 1. For a complete list of supported devices, see the Vivado IP catalog.

- Standalone driver details can be found in the software development kit (SDK) directory (<install directory>/SDK/ 2. <release>/data/embeddedsw/doc/xilinx\_drivers.htm). Linux OS and driver support information is available from the Xilinx Wiki page. jed ver.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

PG304 (v1.0) December 5, 2018 Partial Reconfiguration Bitstream Monitor v1.0

## Overview

Mistakes in bitstream storage, handling, and formatting can cause failures in Partially Reconfigurable designs that can be frustrating and time consuming to debug. Commonly seen problems are:

- Bit files are used instead of bin files

- The system's Partial Reconfiguration Controller (either the PRC core, software, or custom logic) is given the wrong size or address information for the partial bitstreams

- Partial bitstreams have incorrect bit-swapping or endian setting

- Partial bitstreams from the latest implementation run are not used

- The logic communicating with the configuration port is incorrect

One or more Bitstream Monitors can be used to trace the flow of partial bitstreams from storage into the configuration engine. When armed, identifiers embedded at key places in partial bitstreams are extracted are reported by the core. This information can be passed to Vivado HW Debugger using an ILA core to work out what partial bitstream was fetched, if it was fetched in its entirety, and how far through the datapath it went.

This information can also be used by the system for other purposes such as:

- Blocking partial bitstreams that are intended for another static logic

- Blocking partial bitstreams that are not for the Reconfigurable Partition being debugged

- Blocking certain partial bitstreams from being loaded if other system conditions have not been met

## **Feature Summary**

#### **Multiple Protocol Support**

The Bitstream Monitor IP can extract bitstream information from AXI4MM, AXI4-Lite, and ICAP buses. It also provides a "generic" protocol which can be used to attach the monitor to any protocol using some glue logic. The IP can be configured to monitor the AXI4MM and AXI4-Lite Read or Write channels.

The monitor only supports the subset of the AXI4MM protocol that is needed to work with the Partial Reconfiguration Controller IP core.

#### Start and End of Bitstream Reporting

The Bitstream Monitor IP reports whether it is the start or the end of the bitstream that has been seen. This feature is used to ensure that an entire bitstream is delivered to the configuration port.

#### **Configuration Engine Support**

The Bitstream Monitor IP can be configured to monitor bitstreams that have passed through the configuration port and into the configuration engine. This makes use of the AXSS register in the configuration engine, which is visible in the fabric using the USR\_ACCESSE2 primitive.

#### **One Shot and Continuous Arming**

The Bitstream Monitor IP can be programmed at run-time to report all bitstreams it sees, or to just report the next bitstream event (start or end) that it sees. It can be disarmed at any time.

#### **Configurable History Depth and Behaviour**

All observed events are stored in a buffer for later retrieval. The depth of this buffer is configurable, as is the core's behaviour when the buffer becomes full. In this case, the core can be configured to either discard the oldest data from the buffer to make space for the newest data, or it can be configured to discard the newest data.

#### **Multiple Options for Status and Control**

The Partial Reconfiguration Bitstream Monitor can be controlled and queried using signals or an AXI4-Lite interface.

#### Works with Partial Reconfiguration Controller

The subset of AXI4MM supported exactly matches the subset of AXI4MM used by the Partial Reconfiguration Controller IP.

## **Unsupported Features**

#### AXI4MM

The Partial Reconfiguration Bitstream Monitor only supports a subset of the AXI4MM protocol. Specifically:

• Address and ID information is not used.

• Data is read from the bottom 32 bits of the data bus regardless of data bus width, write strobes or starting address.

#### USR\_ACCESS and AXSS

Bitstreams annotated for use with the Partial Reconfiguration Bitstream Monitor set the AXSS register in the configuration engine, which changes the value read through the USR\_ACCESSE2 primitive. Designs that need to use the value in the AXSS register after the first partial bitstream has been loaded may be incompatible with the IP.

## Licensing and Ordering

This Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP module is provided at no additional cost with the Xilinx Vivado<sup>®</sup> Design Suite under the terms of the Xilinx End User License.

For more information about this core, visit the Partial Reconfiguration Bitstream Monitor product web page.

Information about other Xilinx® LogiCORE™ IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx® LogiCORE IP modules and tools, contact your local Xilinx sales representative.

PG304 (v1.0) December 5, 2018 Partial Reconfiguration Bitstream Monitor v1.0

## Chapter 3

## **Product Specification**

### **Operation States**

The IP works in three states:

• Unarmed

In the Unarmed state, the core does not monitor or report events.

Armed Continuous

In the Armed Continuous state, the core reports every event that it detects.

Armed One Shot

In the Armed One Shot state, the core reports the next event that it detects, then reverts to the Unarmed state (an event is either the start or the end of a partial bitstream).

### Identifiers

The IP extracts and reports the following four identifiers from the start and the end of partial bitstreams. See Partial Bitstream Preparation for information on how to annotate partial bitstreams.

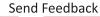

#### Static Partition ID (SP\_ID)

The Static Partition identifier is an FPGA wide identifier that is used to tie a partial bitstream to a particular static bitstream<sup>1</sup>. All partial bitstreams for a particular FPGA should have the same SP\_ID.

If the SP\_ID of the partial bitstream does not match the SP\_ID of the static bitstream then the core flags an error. Other elements in the system could use this information to block the partial bitstream from loading, as loading it could cause damage to the device.

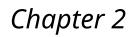

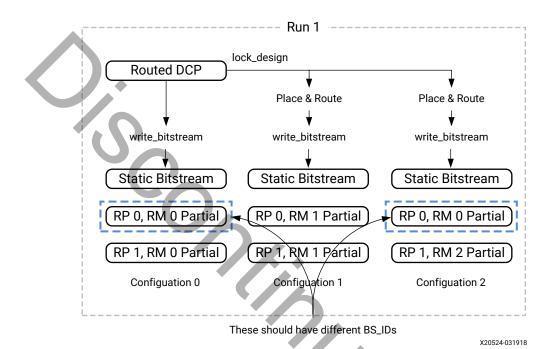

The following figure shows two implementation runs of an example Partial Reconfiguration (PR) project where the static bitstream and partial bitstreams are generated from three implementation configurations (See *Vivado Design Suite User Guide: Partial Reconfiguration* (UG909) for a description of configurations and the PR implementation flow).

1. Partial bitstreams must be generated from the same routed design checkpoint (DCP) as the static bitstream. If they are not, device damage could occur.

Figure 1: Example of a PR Project

To detect the error where bitstreams from both runs are mixed in an application, the SP\_IDs should be set as shown in the following figure.

Figure 2: Setting SP\_ID to detect errors

To provide maximum value, the SP\_ID should be unique to every version of the routed static DCP. For example, the timestamp of the routed static DCP could be used.

The value of SP\_ID that the IP uses for comparison can be set in three ways:

- The static bitstream can have this value set by write\_bitstream so it becomes available through the USR\_ACCESSE2 primitive. The IP can capture this at power on.

- The value can be driven into the core using the ref\_sp\_id\_i port.

• The value can be written into the core using the register interface. Note that the ref\_sp\_id\_i port is still enabled in this case. The value used by the core is the bitwise OR of the ref\_sp\_id\_i port and the register value. It is suggested that the ref\_sp\_id\_i port is left unconnected, or tied to zero, if the register interface is to be used to set the value.

## *Reconfigurable Partition (RP\_ID) and Reconfigurable Module (RM\_ID) IDs*

The RP\_ID and RM\_ID identifiers are used to match a partial bitstream in the design's datapath to a particular Reconfigurable Partition (RP) and Reconfigurable Module (RM) in the functional design description. The core does not interpret these values, and as such, any values that make sense for the application can be used.

The following guidelines may be helpful in choosing RP\_ID and RM\_ID values:

- Each RP should have a unique identifier.

- Each RM should have a unique identifier inside an RP. For example, a single RP shouldn't have two RMs with RM\_ID = 0. However, it is ok for RP 0 to have an RM with RM\_ID = 0, and RP 1 to have an RM with RM\_ID = 0.

As an example, a design with two RPs with two RMs each may have the following identifiers:

#### Table 1: Reconfigurable Partition and Reconfigurable Module IDs

| Reconfigurable Partition | Reconfigurable Module |

|--------------------------|-----------------------|

| SHIFT (RP_ID 0)          | SHIFT_LEFT (RM_ID 0)  |

| SHIFT (RP_ID 0)          | SHIFT_RIGHT (RM_ID 1) |

| COUNT (RP_ID 1)          | COUNT_DOWN (RM_ID 0)  |

| COUNT (RP_ID 1)          | COUNT_UP (RM_ID 1)    |

If a PR Bitstream Monitor monitoring the ICAP bus reported a bitstream with RP\_ID 0 and RM\_ID 1, it would be trivial to identify this as the SHIFT\_RIGHT RM.

**Note:** If the Partial Reconfiguration Controller (PRC) IP is used, then RPs and RMs already have assigned identifiers (VSM ID and RM ID). Using these values would simplify debug. See the *Partial Reconfiguration Controller LogiCORE IP Product Guide* (PG193) for more information.

#### Bitstream Identifier (BS\_ID)

The bitstream identifier serves two purposes:

- To differentiate between clearing and partial bitstreams on UltraScale devices

- To differentiate between partial bitstreams generated for the same RM from different implementation configurations (See Vivado Design Suite User Guide: Partial Reconfiguration (UG909) for a description of configurations and the PR implementation flow.

The following figure shows an example PR project that uses three implementation configurations. RP 0 has two RMs and RP 1 has three RMs. This means one RM will get implemented twice for RP 0 (RM 0 in this example) and will have two separate bitstreams generated. These would both be compatible with the static platform, and could both be used successfully in the design. The BS\_ID is intended to tell them apart.

#### Figure 3: Example Showing the Need for BS\_ID

#### Table 2: IDs for Example Design

| The identifiers for this design could be: |                       |                                                      |  |

|-------------------------------------------|-----------------------|------------------------------------------------------|--|

| Table 2:       IDs for Example Design     |                       |                                                      |  |

| RP                                        | RM                    | BS_ID                                                |  |

| SHIFT (RP_ID 0)                           | SHIFT_LEFT (RM_ID 0)  | 0 (from configuration 0)<br>2 (from configuration 2) |  |

| SHIFT (RP_ID 0)                           | SHIFT_RIGHT (RM_ID 1) | 0                                                    |  |

| COUNT (RP_ID 1)                           | COUNT_DOWN (RM_ID 0)  | 0                                                    |  |

| COUNT (RP_ID 1)                           | COUNT_UP (RM_ID 1)    | 0                                                    |  |

| COUNT (RP_ID 1)                           | COUNT_BY_2 (RM_ID 2)  | 0                                                    |  |

The following guidelines may be helpful in choosing BS\_ID values:

- Bitstream IDs should be unique within an RM, but do not have to be unique between RMs

- In UltraScale devices, the BS\_ID for Clearing Bitstreams could be odd, and even for Partial Bitstreams

- Bitstream IDs could be based on the timestamp of the actual bitstream file

### **Error Detection**

The core can detect the following errors:

- SP\_ID mismatch: This is where the SP\_ID extracted from a bitstream does not match the reference SP\_ID in the core.

- Unexpected Error: This can be caused by the following conditions:

- One or more of the identifiers received at the end of a bitstream do not match the identifiers received at the start of the bitstream.

- The end of a bitstream is seen without first seeing the start of a bitstream (Arming the core part way through a bitstream does not trigger this error).

- The start of a bitstream is seen without seeing the end of the previous bitstream.

## **Control and Status**

The Bitstream Monitor IP provides a signal interface and an AXI4-Lite register interface to control the core. Only one of these can be enabled at a time. It also provides signal and AXI4-Lite register access to the core's status. The AXI4-Lite interface is optional, but the status signals are always present. They can be left unconnected if not required.

## Performance

For full details about performance and resource use, visit the Performance and Resource Use web page.

## **Resource Use**

For full details about performance and resource use, visit the Performance and Resource Use web page.

## **Port Descriptions**

### **Port Names**

The following table lists the port descriptions.

#### Table 3: Port Descriptions

| Port Name             | I/O | Description                                                                                                                                                                                                                                   |

|-----------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk                   | I   | Clock.                                                                                                                                                                                                                                        |

| reset/resetn          | Ι   | Reset. Active-High/Low depending on core configuration.                                                                                                                                                                                       |

| s_axi_ctrl_*          | I,O | AXI4-Lite <sup>1</sup> register interface.                                                                                                                                                                                                    |

| arm                   | Ι   | Assert to enter one of the Armed states.<br>Deassert to enter the Unarmed state.                                                                                                                                                              |

| one_shot              | Ι   | Assert to enter the Armed One Shot state when ${\tt arm}$ is asserted.                                                                                                                                                                        |

|                       |     | Deassert to enter the Armed Continuous state when $a  r  m$ is asserted.                                                                                                                                                                      |

| armed                 | 0   | Asserted when the core has entered one of the Armed states.                                                                                                                                                                                   |

| armed_oneshot         | 0   | Asserted when the core has entered the Armed One Shot state.                                                                                                                                                                                  |

| ref_sp_id_i           |     | The reference SP_ID input. This is only enabled when the HAS_REF_SP_ID_I user parameter is set to TRUE. This is the value that the SP_ID extracted from a bitstream is compared against when determining if there is an SP_ID Mismatch error. |

| ref_sp_id_o           | 0   | The reference SP_ID output. This is only enabled when the HAS_REF_SP_ID_O user parameter is set to TRUE. This signal carries the value of the reference SP_ID in the core. This can either be:                                                |

|                       |     | 1. The value captured from the USR_ACCESSE2 primitive at power on                                                                                                                                                                             |

|                       |     | 2. The value from ref_sp_id_i                                                                                                                                                                                                                 |

|                       |     | <ol> <li>The value from ref_sp_id_i ORd with the value from the register<br/>interface</li> </ol>                                                                                                                                             |

| Live Information      |     |                                                                                                                                                                                                                                               |

| li_avail              | 0   | Asserted for a clock cycle when information is available on the li_* ports.                                                                                                                                                                   |

| li_end                | 0   | 0: The information on the li_* ports relates to the start of a partial bitstream.                                                                                                                                                             |

|                       |     | 1: The information on the li_* ports relates to the end of a partial bitstream.                                                                                                                                                               |

|                       |     | Only valid when li_avail is 1.                                                                                                                                                                                                                |

| li_sp_id              | 0   | The SP_ID extracted from the bitstream.<br>Only valid when li_avail is 1.                                                                                                                                                                     |

| li_rp_id              | 0   | The RP_ID extracted from the bitstream.<br>Only valid when li_avail is 1.                                                                                                                                                                     |

| li_rm_id              | 0   | The RM_ID extracted from the bitstream.<br>OnlyOnly valid when li_avail is 1.                                                                                                                                                                 |

| li_bs_id              | 0   | The BS_ID extracted from the bitstream.<br>li_avail is 1.                                                                                                                                                                                     |

| li_err_sp_id_mismatch | 0   | valid when The SP_ID value extracted from the bitstream does not match<br>the reference SP_ID in the core.<br>Only valid when li_avail is 1.                                                                                                  |

#### Table 3: Port Descriptions (cont'd)

| Port Name                          | I/O | Description                                                                                                                                                                                                                                                                                                |

|------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| li_err_abort                       | 0   | The core has received an abort, either from the protocol_abort input or the registers.<br>Only valid when li_avail is 1.                                                                                                                                                                                   |

| li_err_unexpected                  | 0   | The core has detected an unexpected error (see Error Detection for more information).                                                                                                                                                                                                                      |

|                                    |     | Only valid when li_avail is 1.                                                                                                                                                                                                                                                                             |

| Historic Information               | •   |                                                                                                                                                                                                                                                                                                            |

| hi_avail                           | 0   | Data is available in the historic information buffer.                                                                                                                                                                                                                                                      |

| hi_end                             | 0   | 0: The information on the hi_* ports relates to the start of a partial bitstream.                                                                                                                                                                                                                          |

| 10                                 |     | 1: The information on the hi_* ports relates to the end of a partial bitstream.                                                                                                                                                                                                                            |

|                                    |     | Only valid when hi_avail is 1.                                                                                                                                                                                                                                                                             |

| hi_sp_id                           | 0   | The SP_ID extracted from the bitstream.<br>Only valid when hi_avail is 1.                                                                                                                                                                                                                                  |

| hi_rp_id                           | 0   | The RP_ID extracted from the bitstream.                                                                                                                                                                                                                                                                    |

| m_rp_ia                            |     | Only valid when hi_avail is 1.                                                                                                                                                                                                                                                                             |

| hi_rm_id                           | 0   | The RM_ID extracted from the bitstream.                                                                                                                                                                                                                                                                    |

|                                    | ·   | Only valid when hi_avail is 1.                                                                                                                                                                                                                                                                             |

| hi_bs_id                           | 0   | The BS_ID extracted from the bitstream.<br>Only valid when hi_avail is 1.                                                                                                                                                                                                                                  |

| hi_err_sp_id_mismatch              | 0   | The SP_ID value extracted from the bitstream does not match the reference                                                                                                                                                                                                                                  |

|                                    |     | SP_ID in the core.<br>Only valid when hi_avail is 1.                                                                                                                                                                                                                                                       |

|                                    |     |                                                                                                                                                                                                                                                                                                            |

| hi_err_abort                       | 0   | The core has received an abort, either from the protocol_abort input or the registers.                                                                                                                                                                                                                     |

|                                    |     | Only valid when $hi_avail$ is 1.                                                                                                                                                                                                                                                                           |

| hi_err_unexpected                  | 0   | The core has detected an unexpected error (see Error Detection for more                                                                                                                                                                                                                                    |

|                                    |     | information).<br>Only valid when hi_avail is 1.                                                                                                                                                                                                                                                            |

| hi_read                            | I   | Assert for 1 clock cycle to read one entry from the historic information buffer.                                                                                                                                                                                                                           |

| General Protocol Signals           | I   |                                                                                                                                                                                                                                                                                                            |

| protocol_clock                     | I   | The clock for the interface being monitored. Only enabled when clock domain crossing is requested.                                                                                                                                                                                                         |

| protocol_clock_out                 | 0   | The clock used to extract data from the interface being monitored. Only<br>enabled when clock domain crossing is requested, the core is monitoring<br>the USR_ACCESS protocol, and the core instantiates the USR_ACCESSE2<br>primitive.<br>This signal is provided in order to synchronise protocol_abort. |

| protocol_reset/<br>protocol_resetn | I   | Reset for the data extraction logic. Active high/low depending on core configuration.<br>Enabled when the datapath protocol is AXI4MM, AXI4-Lite or Generic.                                                                                                                                               |

| protocol_abort                     | I   | Assert to abort the monitoring of a bitstream. The core stays in the armed state.                                                                                                                                                                                                                          |

#### Table 3:Port Descriptions (cont'd)

| I          | ICAP CSIB control signal.<br>Enabled when the datapath protocol is ICAP.<br>ICAP RDWRB control signal.<br>Enabled when the datapath protocol is ICAP.<br>ICAP data.<br>Enabled when the datapath protocol is ICAP.                                                                                                                                                                                                                                                                                   |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I          | Enabled when the datapath protocol is ICAP.<br>ICAP RDWRB control signal.<br>Enabled when the datapath protocol is ICAP.<br>ICAP data.                                                                                                                                                                                                                                                                                                                                                               |

| I          | Enabled when the datapath protocol is ICAP.<br>ICAP data.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| T          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| т          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            | USR_ACCESS data.<br>Enabled when the datapath protocol is USR_ACCESS and the core does not<br>instantiate the USR_ACCESSE2 primitive.<br>This port is also enabled when the datapath protocol is not USR_ACCESS,<br>HAS_REF_SP_ID_I is disabled, and the core does not instantiate the<br>USR_ACCESSE2 primitive. In this case, the port should be attached to the<br>USR_ACCESSE2 primitive that exists elsewhere in the design so that the core<br>can get a value for SP_ID at power on.          |

|            | USR_ACCESS data is valid.<br>Enabled when the datapath protocol is USR_ACCESS and the core does not<br>instantiate the USR_ACCESSE2 primitive.<br>This port is also enabled when the datapath protocol is not USR_ACCESS,<br>HAS_REF_SP_ID_I is disabled, and the core does not instantiate the<br>USR_ACCESSE2 primitive. In this case, the port should be attached to the<br>USR_ACCESSE2 primitive that exists elsewhere in the design so that the core<br>can get a value for SP_ID at power on. |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I          | Active high signal to say that the generic_data input has valid data on this clock cycle.<br>Enabled when the datapath protocol is Generic.                                                                                                                                                                                                                                                                                                                                                          |

| Ι          | Enabled when the datapath protocol is Generic.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ol Signals |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I, O       | The AXI monitor interface <sup>1</sup><br>Enabled when the datapath protocol is AXI4MM or AXI4-Lite.                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | I<br>DI Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Notes:

1. For a description of AXI4, AXI4-Lite and AXI Stream signals, see the Vivado Design Suite AXI Reference Guide (UG1037).

## **Register Space**

The PR Bitstream Monitor's register space is summarized in the following table:

#### Table 4: Register Names

| Address<br>Space<br>Offset | Name      | Description                                                           |  |

|----------------------------|-----------|-----------------------------------------------------------------------|--|

| 00h                        | ARM       | Arm/Disarm the core                                                   |  |

| 04h                        | ABORT     | Abort the monitoring for any ongoing bitstream                        |  |

| 08h                        | REF_SP_ID | Set the Reference SP_ID                                               |  |

| 10h                        | ARMED     | Get the state of the core (Unarmed, Armed Continuous, Armed One Shot) |  |

| 14h                        | HI_STATUS | The first status entry in the historical information status buffer    |  |

| 18h                        | HI_SP_ID  | The SP_ID entry in the historical information status buffer           |  |

| 1Ch                        | HI_RP_ID  | The RP_ID entry in the historical information status buffer           |  |

| 20h                        | HI_RM_ID  | The RM_ID entry in the historical information status buffer           |  |

| 24h                        | HI_BS_ID  | The BS_ID entry in the historical information status buffer           |  |

## Arm Control Register

The Arm Control Register is used to arm and disarm the core. All fields are R/W and reset to 0x0. Note that the values read back do not represent the state of the core, only what has been requested. The Armed Status Register must be used to get the state of the core.

#### Table 5: Arm Control Register

| Bit  | Name     | Description                                                                          |

|------|----------|--------------------------------------------------------------------------------------|

| 31:2 | Reserved | Reserved                                                                             |

| 1    | ONE_SHOT | 1: Arm One Shot<br>0: Arm Continuous<br>These bits only have an effect when ARM is 1 |

| 0    | ARM      | 1: Arm the core<br>0: Disarm the core                                                |

### **Abort Control Register**

The Abort Control Register is write only and resets to 0x0.

#### Table 6: Abort Control Register

| Bits | Name     | Description                             |

|------|----------|-----------------------------------------|

| 31:1 | Reserved | Reserved                                |

| 0    | ABORT    | 1: Abort the monitoring<br>0: No effect |

### **Reference SP\_ID Register**

The Reference SP\_ID Register is used to set the SP\_ID value that the core uses to generate sp\_id\_mismatch errors.

If the HAS\_REF\_SP\_ID\_I User Parameter is set to FALSE, then this register is read only. In this case, the value read is the value set by the USR\_ACCESSE2 primitive.

If the HAS\_REF\_SP\_ID\_I User Parameter is set to TRUE, then this register can be written. However, the value written to this register is bitwise ORd with the value on the  $ref_sp_id_i$  port before being used in the core. The value read from this register is the bitwise ORd version.

It is recommended that the  $ref_{sp-id_i}$  port is left unconnected, or connected to all-zero, if this register is going to be used.

Table 7: SP\_ID Register Bit Definition

| Bits  | Name      | Description               |

|-------|-----------|---------------------------|

| 31:W  | Reserved  | Reserved                  |

| W-1:0 | REF_SP_ID | The reference SP_ID value |

*Note*: W is set by the STS\_SP\_ID\_WIDTH User Parameter.

### Armed Status Register

The Armed Status Register is read only and resets to 0x0.

Table 8: Armed Status Register Bit Definitions

| Bits | Name     | Description                                                                                                       |  |

|------|----------|-------------------------------------------------------------------------------------------------------------------|--|

| 31:2 | Reserved | Reserved                                                                                                          |  |

| 1    | ONE_SHOT | 1: The core is Armed One Shot<br>0: The core is Armed Continuous<br>These bits only have meaning when ARMED is 1. |  |

| 0    | ARMED    | 1: The core is Armed<br>0: The core is Disarmed                                                                   |  |

## **Historical Information Status Register**

The Historical Information Status Register is read only, and all fields reset to 0. Reading from this register updates the values in the following registers, and removes the entry from the Historical Information buffer:

- HI\_SP\_ID

- HI\_RP\_ID

- HI\_RM\_ID

- HI\_BS\_ID

#### Table 9: Historical Information Status Register Bit Definitions

| Bits | Name                                    | Description                                                                                    |

|------|-----------------------------------------|------------------------------------------------------------------------------------------------|

| 31:5 | Reserved                                | Reserved                                                                                       |

| 4    | HI_ERR_SP_ID_MISMATCH                   | 1: The SP_ID value extracted from the bitstream did not match the reference SP_ID in the core. |

|      | $\sim$                                  | 0: The SP_ID value extracted from the bitstream matched the reference SP_ID in the core.       |

| 3    | HI_ERR_UNEXPECTED                       | 1: The core detected an unexpected error.                                                      |

|      |                                         | 0: The core did not detect an unexpected error.                                                |

|      |                                         | (see Error Detection for more information).                                                    |

| 2    | HI_ERR_ABORT                            | 1: The core received an abort, either from the protocol_abort input or the registers.          |

|      |                                         | 0: The core did not receive an abort.                                                          |

| 1    | HI_END                                  | 1: The information on the HI_* registers relates to the end of a partial bitstream.            |

|      |                                         | 0: The information in the Hi_* registers relates to the start of a partial bitstream.          |

| 0    | HI_AVAIL                                | 1: Data is available in the historic information buffer.                                       |

|      | , i i i i i i i i i i i i i i i i i i i | 0: No data available.                                                                          |

## Historical Information SP\_ID Register

The Historical Information SP\_ID Register is read only, and all fields reset to 0.

#### Table 10: Historical Information SP\_ID Bit Definitions

| Bits  | Name     | Description                            |  |  |

|-------|----------|----------------------------------------|--|--|

| 31:W  | Reserved | Reserved                               |  |  |

| W-1:0 | HI_SP_ID | The SP_ID extracted from the bitstream |  |  |

|       | •        |                                        |  |  |

*Note*: W is set by the STS\_SP\_ID\_WIDTH User Parameter.

### Historical Information RP\_ID Register

The Historical Information RP\_ID Register is read only, and all fields reset to 0.

#### Table 11: Historical Information RP\_ID Bit Definitions

| Bits  | Name     | Description                            |  |

|-------|----------|----------------------------------------|--|

| 31:W  | Reserved | Reserved                               |  |

| W-1:0 | HI_RP_ID | The RP_ID extracted from the bitstream |  |

*Note*: W is set by the STS\_RP\_ID\_WIDTH User Parameter.

### Historical Information RM\_ID Register

The Historical Information RM\_ID Register is read only, and all fields reset to 0.

Table 12: Historical Information RM\_ID Bit Definitions

| Bits  | Name     | Description                            |  |

|-------|----------|----------------------------------------|--|

| 31:W  | Reserved | Reserved                               |  |

| W-1:0 | HI_RM_ID | The RM_ID extracted from the bitstream |  |

*Note*: W is set by the STS\_RM\_ID\_WIDTH User Parameter.

## Historical Information BS\_ID Register

The Historical Information BS\_ID Register is read only, and all fields reset to 0.

#### Table 13: Historical Information BS\_ID Bit Definitions

| Bits  | Name     | Description                            |

|-------|----------|----------------------------------------|

| 31:W  | Reserved | Reserved                               |

| W-1:0 | HI_BS_ID | The BS_ID extracted from the bitstream |

*Note*: W is set by the STS\_BS\_ID\_WIDTH User Parameter.

## Chapter 4

## Designing with the Core

## USR\_ACCESS Primitive

The following configurations of the PR Bitstream Monitor core require information from the USR\_ACCESSE2 primitive:

- When the datapath protocol is set to USR\_ACCESS

- When the reference SP\_ID is to be read from the static bitstream (HAS\_REF\_SP\_ID\_I = FALSE)

The USR\_ACCESSE2 primitive can only be instantiated once in a design, so the IP offers the option to instantiate it or not. If the core instantiates it, no other core in the system can do so. If the core does not instantiate it, ports are made available on the core boundary to import the required information.

## **Bitstream Growth**

Annotating a bitstream with identifiers for use with the PR Bitstream Monitor core adds 29 words (116 bytes) to the bitstream size. This may require changes to the addresses where the bitstreams are stored. Any system component that must know the address and/or size of a partial bitstream (for example, the Partial Reconfiguration Controller) has to be updated with the new addresses and/or sizes. It is useful to add the identifiers to the partial bitstreams during development, even if the Bitstream Monitor is not being used in a particular implementation run.

## Clocking

The core has one or two clock inputs, depending on the configuration.

- clk: The main core clock

- protocol\_clock : Used to clock the protocol decode logic when DP\_HAS\_CDC is set to TRUE

In cases where the core instantiates the USR\_ACCESSE2 primitive, decodes the USR\_ACCESS protocol, and has DP\_HAS\_CDC set to FALSE, carefully ensure that the core's clk input is identical to the configuration clock that is output from the USR\_ACCESSE2 primitive. If not, data from the USR\_ACCESSE2 primitive may be sampled incorrectly. If DP\_HAS\_CDC is set to TRUE, the protocol\_clock\_out output is enabled which provides access to the USR\_ACCESSE2 primitive's CFGCLK output. This should be used to synchronise the generation of the protocol\_abort input.

PG304 (v1.0) December 5, 2018 Partial Reconfiguration Bitstream Monitor v1.0

## Chapter 5

## **Design Flow Steps**

This section describes customizing and generating the core, constraining the core, and the simulation, synthesis, and implementation steps that are specific to this IP core. More detailed information about the standard Vivado<sup>®</sup> design flows and the IP integrator can be found in the following Vivado Design Suite user guides:

- Vivado Design Suite User Guide: Designing IP Subsystems using IP Integrator (UG994)

- Vivado Design Suite User Guide: Designing with IP (UG896)

- Vivado Design Suite User Guide: Getting Started (UG910)

- Vivado Design Suite User Guide: Logic Simulation (UG900)

## **Customizing and Generating the Core**

This section includes information about using Xilinx<sup>®</sup> tools to customize and generate the core in the Vivado<sup>®</sup> Design Suite.

If you are customizing and generating the core in the Vivado IP integrator, see the Vivado Design Suite User Guide: Designing IP Subsystems using IP Integrator (UG994) for detailed information. IP integrator might auto-compute certain configuration values when validating or generating the design. To check whether the values do change, see the description of the parameter in this chapter. To view the parameter value, run the validate\_bd\_design command in the Tcl console.

You can customize the IP for use in your design by specifying values for the various parameters associated with the IP core using the following steps:

- 1. Select the IP from the IP catalog.

- 2. Double-click the selected IP or select the Customize IP command from the toolbar or rightclick menu.

For details, see the Vivado Design Suite User Guide: Designing with IP (UG896) and the Vivado Design Suite User Guide: Getting Started (UG910).

Figures in this chapter are illustrations of the Vivado IDE. The layout depicted here might vary from the current version.

Send Feedback

## **Global Options Tab**

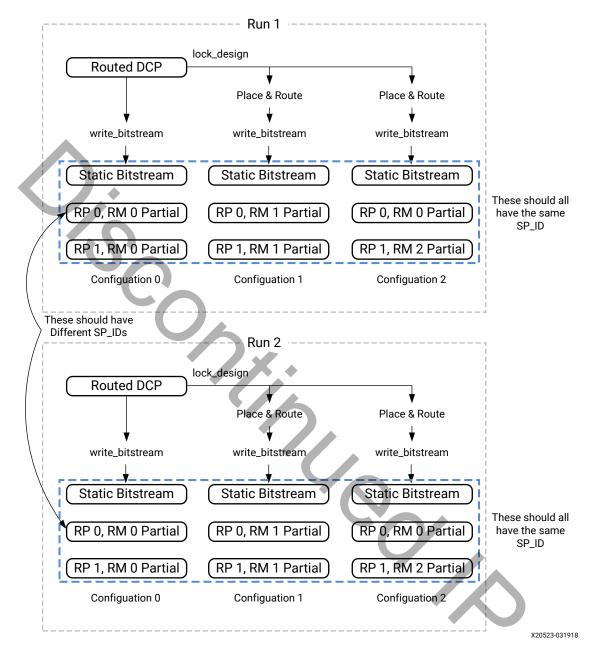

The parameters in the Global Options tab are shown in the following figure.

| Reset Active Level 0                                                                                                                      | ✓ 🗌 Instanti                                               | iate the USR_ACCESS F          | Primitive            |                                         |                  |   |          |

|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------|----------------------|-----------------------------------------|------------------|---|----------|

| Control Options                                                                                                                           |                                                            |                                |                      | Status Options                          |                  |   |          |

| Control Interface Type                                                                                                                    | ٥                                                          | ignal 🗸 🗸                      |                      | SP ID Width                             | 32               | Ø | [1 - 32] |

| Control Interface Address Wi                                                                                                              | dth 33                                                     | 2                              | [7 - 64]             | RP ID Width                             | 32               | ٢ | [1 - 32] |

| 😟 Has User Setable Refere                                                                                                                 | nee St ID Input                                            |                                |                      | FM ID Width                             | 32               | ٢ | [1 - 32] |

| I Has Reference SP ID Out                                                                                                                 | put                                                        |                                |                      | BS ID Width                             | 32               | Ø | [1 - 32] |

|                                                                                                                                           |                                                            |                                |                      | History Buffer: Implementation          | Distributed RAM  | * |          |

|                                                                                                                                           |                                                            |                                |                      | History Buffer: Depth                   | 16               | ~ |          |

|                                                                                                                                           |                                                            |                                |                      | History Buffer: Behavior when full      | Discard New Data | ~ |          |

| 50 N                                                                                                                                      |                                                            |                                |                      |                                         |                  |   |          |

| atapath Options                                                                                                                           | -                                                          |                                |                      |                                         |                  |   |          |

| Datapath Protocol                                                                                                                         | AX34MM                                                     |                                | × +                  | ~                                       |                  |   |          |

| Datapath Reset Active Level                                                                                                               | 0                                                          |                                |                      | *                                       |                  |   |          |

|                                                                                                                                           |                                                            |                                |                      |                                         |                  |   |          |

| Data format                                                                                                                               | Little Endian with                                         | no Bitswapping. Synt           | word AA9955          | 66 appears as AA995566 🗸                |                  |   |          |

| Data format                                                                                                                               | Little Endian with                                         | no Bitswapping. Synt           | word AA9955          | 66 appears as AA995566 🗸                |                  |   |          |

|                                                                                                                                           | Little Endian with<br>Distributed RAM                      | no Bitswapping. Synt           | word AA9955          | 66 appears as AA995566 🗸                |                  |   |          |

| Has CDC                                                                                                                                   |                                                            | no Bitswapping. Synd           | word A40955          | €6 appears as AA995566 ↓<br>↓           |                  |   |          |

| CDC FIFO: Type                                                                                                                            | Distributed RAM                                            | no Bitswapping. Synt           | word A40953          | €6 appears as AA995566 ↓<br>↓<br>↓<br>↓ |                  |   |          |

| CDC FIFO: Type                                                                                                                            | Distributed RAM                                            | no Bitswapping. Synt           | word AA9955          | 66 appears as AA995566 v                |                  |   |          |

| CDC FIFO: Type                                                                                                                            | Distributed RAM<br>32<br>6                                 | no Bitswapping. Synd           | word A43955          | €6 appears as AA995566                  |                  |   |          |

| Has CDC CDC FIFO: Type CDC FIFO: Depth Number of CDC Stages                                                                               | Distributed RAM<br>32<br>6                                 | no Bitswapping. Synt           | word AA9953          | 66 appears as AA995566 v                |                  |   |          |

| Has CDC CDC FIFO: Type CDC FIFO: Depth Number of CDC Stages Reset Active Level                                                            | Distributed RAM<br>32<br>6                                 |                                |                      | €6 appears as AA995566 ↓<br>↓<br>↓<br>↓ |                  |   |          |

| Has CDC<br>CDC FIFO: Type<br>CDC FIFO: Depth<br>Number of CDC Stages<br>Reset Active Level<br>This option sets the                        | Distributed RAM<br>32<br>6<br>e active lev                 | rel of the cor                 | e reset.             |                                         |                  |   |          |

| Has CDC<br>CDC FIFO: Type<br>CDC FIFO: Depth<br>Number of CDC Stages<br>Reset Active Level<br>This option sets the<br>• 0: The reset is a | Distributed RAM<br>32<br>6<br>e active lev<br>active-Low a | vel of the cor<br>and the rese | e reset.<br>etn sign | al is enabled                           |                  |   |          |

| Has CDC<br>CDC FIFO: Type<br>CDC FIFO: Depth<br>Number of CDC Stages<br>Reset Active Level<br>This option sets the                        | Distributed RAM<br>32<br>6<br>e active lev<br>active-Low a | vel of the cor<br>and the rese | e reset.<br>etn sign | al is enabled                           |                  |   |          |

Figure 4: Global Options Tab

This option controls whether the USR\_ACCESSE2 primitive is instantiated by the core.

- TRUE: The USR\_ACCESSE2 primitive is instantiated

- FALSE: The USR\_ACCESSE2 primitive is not instantiated

#### **Control Interface Type**

This option sets the control interface type. Valid values are:

- Signal

- AXI4Lite

#### **Control Interface Address Width**

This option sets the address width used by the AXI4-Lite register interface. Valid values are 7 to 64 inclusive.

#### Has User Settable Reference SP\_ID Input

This option is used to decide if the core will get the reference value of SP\_ID from the USR\_ACCESSE2 primitive, or from core inputs.

- TRUE: The reference SP\_ID will be taken from the ref\_sp\_id\_i port or the register interface

- FALSE: The reference SP\_ID will be taken from the USR\_ACCESSE2 primitive

#### Has Reference SP\_ID Output

This option enables or disables the ref\_sp\_id\_o output.

- TRUE: Enable the output

- FALSE: Disable the output

#### SP\_ID\_WIDTH

This option sets the width of the SP\_ID identifier. Valid values are 1 to 32 inclusive.

#### RP\_ID\_WIDTH

This option sets the width of the RP\_ID identifier. Valid values are 1 to 32 inclusive.

#### RM\_ID\_WIDTH

This option sets the width of the RM\_ID identifier. Valid values are 1 to 32 inclusive.

#### BS\_ID\_WIDTH

This option sets the width of the BS\_ID identifier. Valid values are 1 to 32 inclusive.

#### **History Buffer Implementation**

This option sets the type of memory used to implement the History Buffer. Valid options are:

- Distributed RAM

- Block RAM

#### History Buffer Depth

This option sets the number of entries in the History Buffer. Valid values are:

- 16

- 32

- 64

- 128

- 256

- 512

- 1024

- 2048

- 4096 •

- 8192

- 16384

- 32768

- 65536

- 131072

# 300% **History Buffer Behavior When Full**

This option specifies what will happen when there's new data for the History Buffer and it is already full. Valid options are:

- Discard new data: The new data is discarded

- Discard old data: The oldest data in the buffer is discarded

#### Datapath Protocol

This option specifies the protocol of the bus that the core will be connected to. Valid options are:

- AXI4MM

- AXI4Lite

- ICAP

- USR ACCESS

- GENERIC

The Generic protocol is provided as a way of attaching the monitor to protocols that aren't natively supported by the core.

#### **Datapath Active Reset Level**

This option sets the active level of the datapath's reset.

- 0: The reset is active-Low

- 1: The reset is active-High

#### **Data Format**

This options tells the core how to interpret the data. Valid options are:

- Little endian with no bitswapping

- Little endian with bitswapping

- Big endian with no bitswapping

- Big endian with bitswapping

#### Has CDC

This option enables or disables the core's clock domain crossing logic.

- TRUE: Enable clock domain crossing

- FALSE: Disable clock domain crossing

#### CDC FIFO Type

This option sets the type of memory used to implement the clock domain crossing FIFO. Valid options are: Ç

- Distributed RAM

- Block RAM

#### **CDC FIFO Depth**

This option sets the number of entries in the clock domain crossing FIFO. Valid values are:

- 32

- 64

- 128

- 256

- 512

- 1024

- 2048

- 4096

- 8192

- 16384

- 32768

- 65536

- 131072

#### Number of CDC stages

This option sets the number of stages in the clock domain crossing synchronisers. Valid values are 2 to 8 inclusive.

### **AXI4MM Options Tab**

The parameters in the AXI4MM Options tab are shown in the following figure and are described in this section.

| Figure 5: AXI4MM Options Tab                      |

|---------------------------------------------------|

| Global Options AXI4MM Options                     |