# MIPI CSI-2 Receiver Subsystem v3.0

# LogiCORE IP Product Guide

**Vivado Design Suite**

PG232 April 4, 2018

# **Table of Contents**

## **IP Facts**

| Chapter 1: Overview                      |    |

|------------------------------------------|----|

| Sub-Core Details                         | 6  |

| Applications                             | 11 |

| Unsupported Features                     | 12 |

| Licensing and Ordering                   | 12 |

| Chapter 2: Product Specification         |    |

| Standards                                | 13 |

| Resource Utilization                     |    |

| Port Descriptions                        | 13 |

| Register Space                           | 17 |

| Chapter 3: Designing with the Subsystem  |    |

| General Design Guidelines                | 28 |

| Shared Logic                             | 28 |

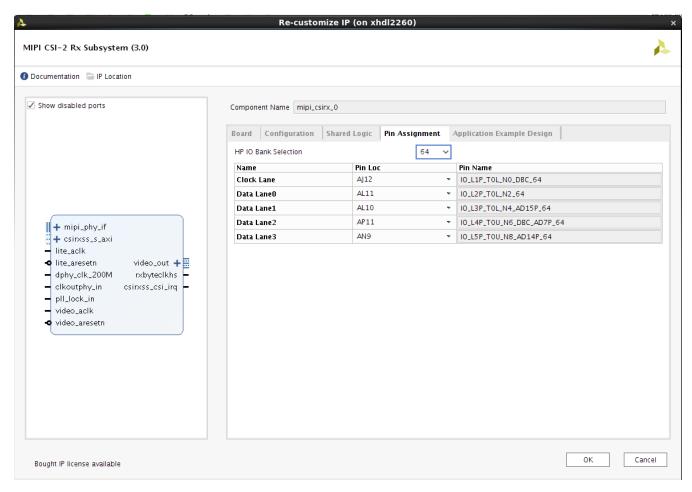

| I/O Planning                             | 32 |

| Clocking                                 |    |

| Resets                                   | 35 |

| Protocol Description                     | 36 |

| Chapter 4: Design Flow Steps             |    |

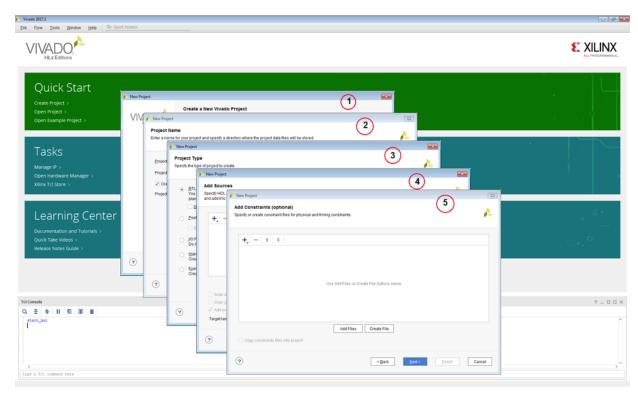

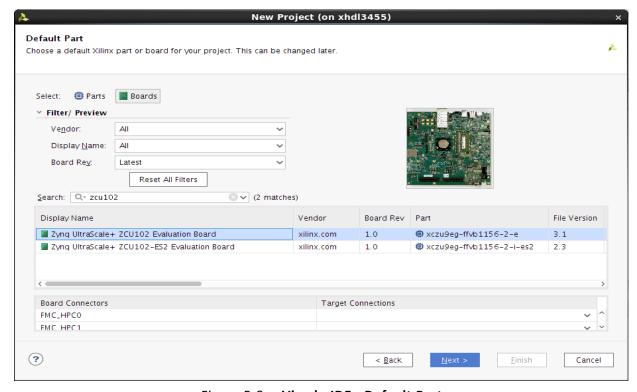

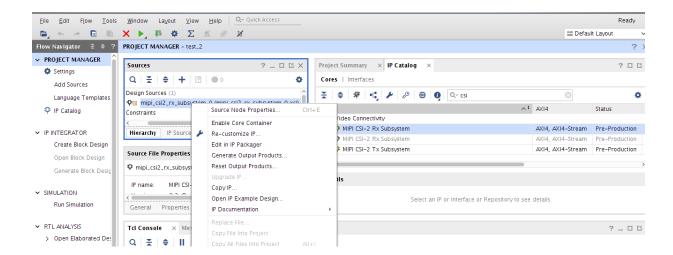

| Customizing and Generating the Subsystem | 39 |

| Constraining the Subsystem               | 48 |

| Simulation                               | 49 |

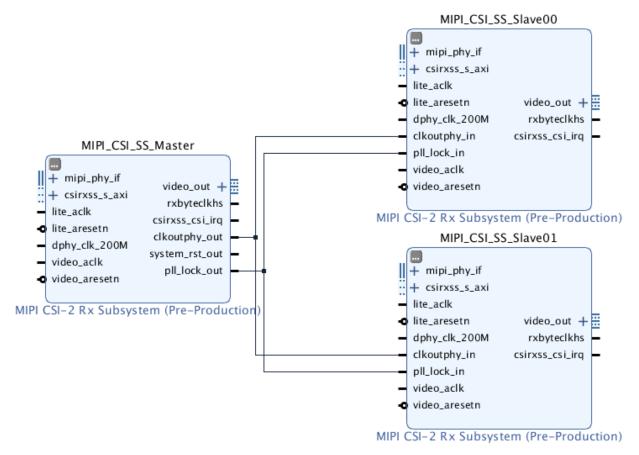

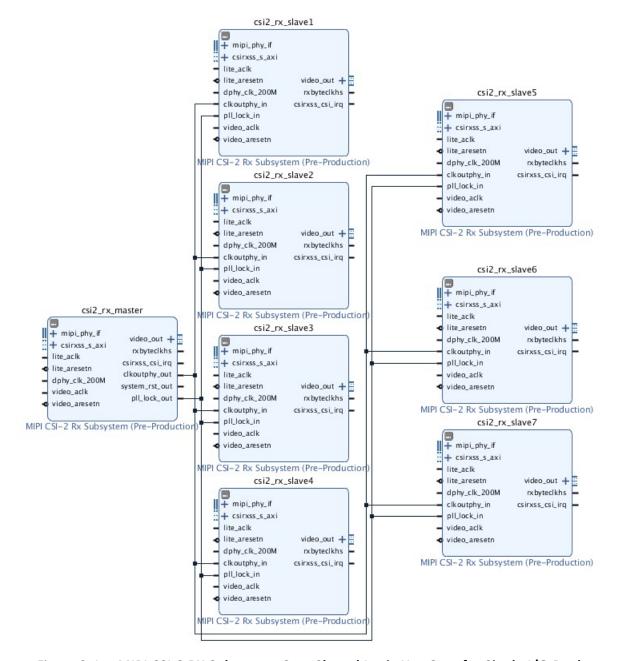

| Synthesis and Implementation             | 50 |

| Chapter 5: Application Example Design    |    |

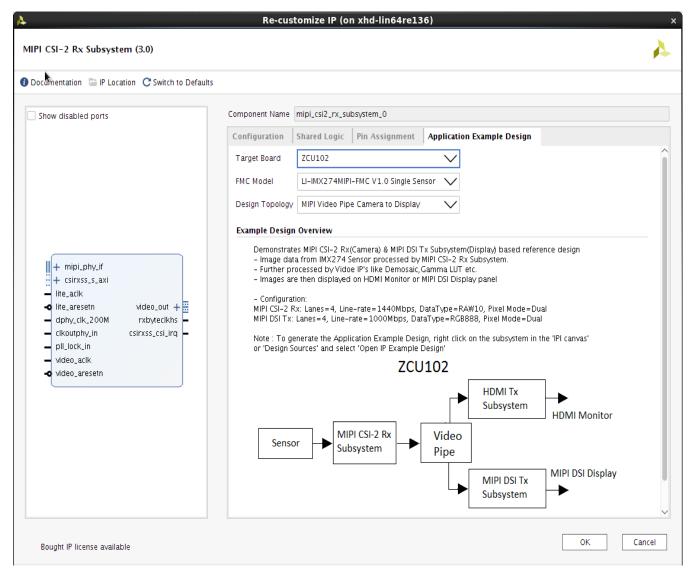

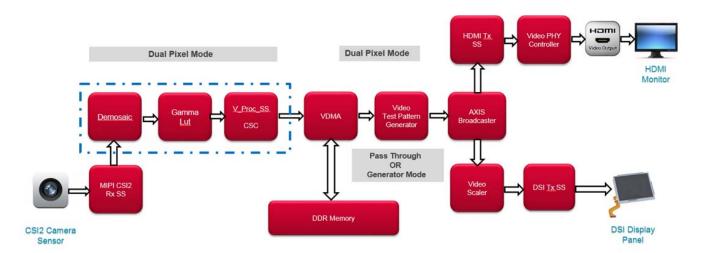

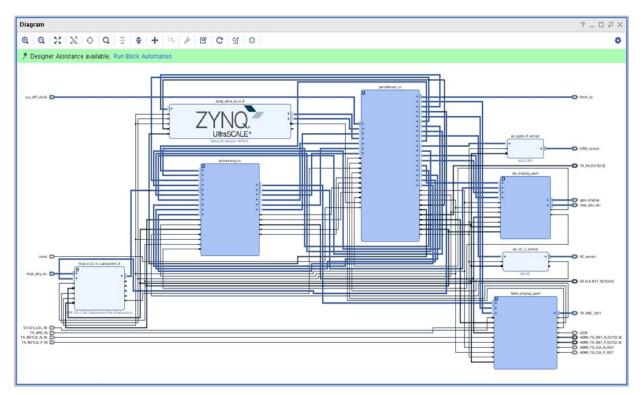

| Application Example Design Overview      | 51 |

| Setup Details 5                          |    |

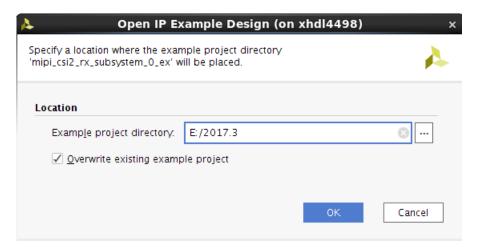

| Implementing the Example Design          | 58 |

| Appendix A: Verification, Compliance, and Interoperability |    |

|------------------------------------------------------------|----|

| Hardware Validation                                        | 66 |

| Appendix B: Debugging                                      |    |

| Finding Help on Xilinx.com                                 | 68 |

| Debug Tools                                                | 69 |

| Hardware Debug                                             | 70 |

| Interface Debug                                            | 71 |

| Appendix C: Additional Resources and Legal Notices         |    |

| Xilinx Resources                                           | 74 |

| Documentation Navigator and Design Hubs                    | 74 |

| References                                                 | 74 |

| Revision History                                           | 76 |

| Please Read: Important Legal Notices                       | 77 |

www.xilinx.com

## Introduction

The Mobile Industry Processor Interface (MIPI) Camera Serial Interface (CSI-2) RX subsystem implements a CSI-2 receive interface according to the MIPI CSI-2 standard, v1.1 [Ref 1]. The subsystem captures images from MIPI CSI-2 camera sensors and outputs AXI4-Stream video data ready for image processing. The subsystem allows fast selection of the top level parameters and automates most of the lower level parameterization. The AXI4-Stream video interface allows a seamless interface to other AXI4-Stream-based subsystems.

## **Features**

- Support for 1 to 4 D-PHY lanes

- Line rates ranging from 80 to 1500 Mb/s

- Multiple Data Type support (RAW, RGB, YUV)

- AXI IIC support for Camera Control Interface (CCI)

- Filtering based on Virtual Channel Identifier

- Support for 1, 2 or 4 pixels per sample at the output as defined in the Xilinx AXI4-Stream Video IP and System Design Guide (UG934) [Ref 2] format

- AXI4-Lite interface for register access to configure different subsystem options

- Dynamic selection of active lanes within the configured lanes during subsystem generation.

- Interrupt generation to indicate subsystem status information

- Internal D-PHY allows direct connection to image sources

|                                           | IP Facts Table                                                                                  |  |  |  |  |  |  |  |  |  |  |  |

|-------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

|                                           | Subsystem Specifics                                                                             |  |  |  |  |  |  |  |  |  |  |  |

| Supported<br>Device Family <sup>(1)</sup> | UltraScale+™,<br>Zynq® UltraScale+ MPSoC,<br>Zynq®-7000 All Programmable SoC,<br>7 Series FPGAs |  |  |  |  |  |  |  |  |  |  |  |

| Supported User<br>Interfaces              | AXI4-Lite, AXI4-Stream                                                                          |  |  |  |  |  |  |  |  |  |  |  |

| Resources                                 | Performance and Resource Utilization web page                                                   |  |  |  |  |  |  |  |  |  |  |  |

| P                                         | rovided with Subsystem                                                                          |  |  |  |  |  |  |  |  |  |  |  |

| Design Files                              | esign Files Encrypted RTL ample Design Vivado IP Integrator                                     |  |  |  |  |  |  |  |  |  |  |  |

| Example Design                            | Vivado IP Integrator                                                                            |  |  |  |  |  |  |  |  |  |  |  |

| Test Bench                                | Not Provided                                                                                    |  |  |  |  |  |  |  |  |  |  |  |

| Constraints File                          | XDC                                                                                             |  |  |  |  |  |  |  |  |  |  |  |

| Simulation<br>Model                       | Not Provided                                                                                    |  |  |  |  |  |  |  |  |  |  |  |

| Supported<br>S/W Driver <sup>(2)</sup>    | Standalone and Linux                                                                            |  |  |  |  |  |  |  |  |  |  |  |

|                                           | Tested Design Flows <sup>(3)</sup>                                                              |  |  |  |  |  |  |  |  |  |  |  |

| Design Entry                              | Vivado® Design Suite                                                                            |  |  |  |  |  |  |  |  |  |  |  |

| Simulation                                | For supported simulators, see the Xilinx Design Tools: Release Notes Guide.                     |  |  |  |  |  |  |  |  |  |  |  |

| Synthesis                                 | Vivado Synthesis                                                                                |  |  |  |  |  |  |  |  |  |  |  |

|                                           | Support                                                                                         |  |  |  |  |  |  |  |  |  |  |  |

| Provided b                                | y Xilinx at the Xilinx Support web page                                                         |  |  |  |  |  |  |  |  |  |  |  |

#### Notes:

- For a complete list of supported devices, see the Vivado IP catalog.

- Standalone driver details can be found in the SDK directory (<install\_directory>/SDK/<release>/data/embeddedsw/doc/ xilinx\_drivers.htm). Linux OS and driver support information is available from the Xilinx Wiki page.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

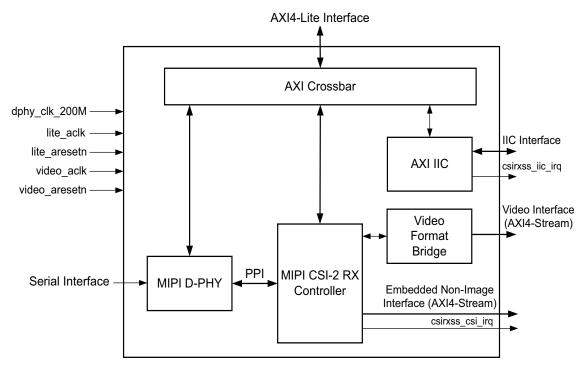

The MIPI CSI-2 RX subsystem allows you to quickly create systems based on the MIPI protocol. It interfaces between MIPI-based image sensors and an image sensor pipe. An internal high speed physical layer design, D-PHY, is provided that allows direct connection to image sources. The top level customization parameters select the required hardware blocks needed to build the subsystem. Figure 1-1 shows the subsystem architecture.

Figure 1-1: Subsystem Architecture

The subsystem consists of the following sub-cores:

- MIPI D-PHY

- MIPI CSI-2 RX Controller

- AXI Crossbar

- · Video Format Bridge

- AXI IIC

## **Sub-Core Details**

#### MIPI D-PHY

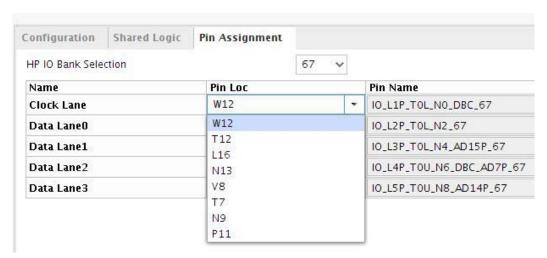

The MIPI D-PHY IP core implements a D-PHY RX interface and provides PHY protocol layer support compatible with the CSI-2 RX interface. See the MIPI D-PHY LogiCORE IP Product Guide (PG202) [Ref 3] for details. MIPI D-PHY implementation differs for the UltraScale+ devices and the 7 Series devices with respect to I/O.

For UltraScale+ devices, the Vivado IDE provides a Pin Assignment Tab to select the required I/O. However, for the 7 series devices the clock capable I/O should be selected manually. In addition, the 7 series devices do not have a native MIPI IOB support. You will have to target either HR bank I/O or HP bank I/O for the MIPI IP implementation. For more information on MIPI IOB compliant solution and guidance, refer *D-PHY Solutions* (XAPP894) [Ref 15].

## MIPI CSI-2 RX Controller

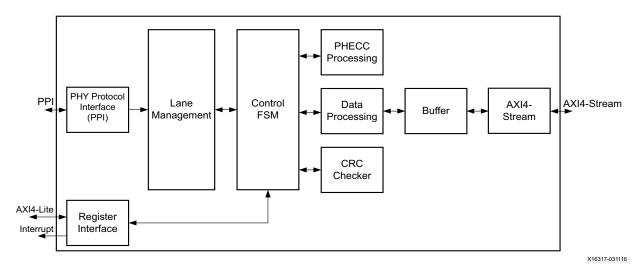

The MIPI CSI-2 RX Controller core consists of multiple layers defined in the MIPI CSI-2 RX 1.1 specification, such as the lane management layer, low level protocol and byte to pixel conversion.

The MIPI CSI-2 RX Controller core receives 8-bit data per lane, with support for up to 4 lanes, from the MIPI D-PHY core through the PPI. As shown in Figure 1-1 the byte data received on the PPI is then processed by the low level protocol module to extract the real image information. The final extracted image is made available to the user/processor interface using the AXI4-Stream protocol. The lane management block always operates on 32-bit data received from PPI irrespective number of lanes.

Figure 1-2: MIPI CSI-2 RX Controller Core

#### Features of this core include:

- 1–4 lane support, with register support to select active lanes (the actual number of available lanes to be used)

- Short and long packets with all word count values supported

- Primary and many secondary video formats supported

- Data Type (DT) interleaving

- Virtual Channel Identifier (VC) interleaving

- Combination of Data Type and VC interleaving

- Multi-lane interoperability

- Error Correction Code (ECC) for 1-bit error correction and 2-bit error detection in packet header

- CRC check for payload data

- Long packet ECC/CRC forwarding capability for downstream IPs

- Maximum data rate of 1.5 Gb/s

- Pixel byte packing based on data format

- AXI4-Lite interface to access core registers

- Low power state detection

- Error detection (D-PHY Level Errors, Packet Level Errors, Protocol Decoding Level Errors)

- AXI4-Stream interface with 32/64-bit TDATA width support to offload pixel information externally

- Interrupt support for indicating internal status/error information

As shown in Table 1-1 the embedded non-image (with data type code 0x12) AXI4-Stream interface data width is selected based on the Data Type selected.

Table 1-1: Embedded Non-Image AXI4-Stream Interface TDATA Widths

| Data Type (DT) | AXI4-Stream Interface TDATA Width |

|----------------|-----------------------------------|

| RAW6           | 32                                |

| RAW7           | 32                                |

| RAW8           | 32                                |

| RAW10          | 64                                |

| RAW12          | 64                                |

| RAW14          | 64                                |

| All RGB        | 64                                |

| YUV 422 8bit   | 64                                |

Abrupt termination events such as a soft reset, disabling a core while a packet is being written to the line buffer, or a line buffer full condition results in early termination. The termination is implemented by assertion of EOL on the video interface or TLAST and TUSER[1] on the embedded non-image interface, based on the current long packet being processed.

## **ECC/CRC Forwarding**

Sideband signals of AXI4-Stream interface [Include/Exclude Video Format Bridge and Embedded non-image interface] report ECC and CRC data received from the source [sensor] to downstream IPs. This allows to re-calculate ECC/CRC by the downstream IPs in certain functional safety applications. See Port Descriptions for details on signal mapping.

In error scenarios like abrupt termination due to soft reset, disabling the core while packet transfer in progress, line buffer in full condition, word count of received packet is greater than the actual payload, these sideband signals do not report the correct ECC and CRC.

#### **AXI Crossbar**

The AXI Crossbar core is used in the subsystem to route AXI4-Lite requests to corresponding sub-cores based on the address. See the AXI Interconnect LogiCORE IP Product Guide [Ref 4] for details.

## **Video Format Bridge**

The Video Format Bridge core uses the user-selected VC and Data Type information to filter only the required AXI4-Stream data beats. This AXI4-Stream data is further processed based on the Data Type information and the output is based on the requested number of pixels per beat. The output interface adheres to the protocol defined in the AXI4-Stream Video IP and System Design Guide (UG934) [Ref 2].

The Video Format Bridge core processes the data type selected in the Vivado Integrated Design Environment (IDE) and filters out all other data types except for RAW8 and User Defined Byte-based Data types (0x30 to 0x37) received from the CSI-2 RX Controller.

Irrespective of the Vivado IDE selection, RAW8 and User Defined Byte-based Data types are always processed by the Video Format Bridge core. This allows multiple data-type support, one main data-type from the Vivado IDE for pixel data and a User Defined Byte-based Data type for metadata. When multiple data types are transferred (for example, RAW10 and User Defined Byte-based Data) the actual placement pixel data bits are defined in the AXI4-Stream Video IP and System Design Guide (UG934) [Ref 2].

For unaligned transfers there is no way to specify the partial final output (TKEEP) for the output interface. Ensure that you take this into consideration and discard the unintended bytes in the last beats when there are un-aligned transfers.

#### video out Port Width

The width of the data port in the video\_out interface depends on the data type selected and number of pixels per beat selected. The width is a maximum of the RAW8 and the data type selected in the Vivado IDE multiplied by number of pixels per beat. This is then rounded to the nearest byte boundary as per the AXI4-Stream protocol.

#### Example 1: RAW10 and Two Pixels per Clock Selected in the Vivado IDE

- Single pixel width of RAW10 = 10

- Single pixel width of RAW8 = 8

For the selected two pixels per clock, the effective pixels widths are 20 and 16 for RAW10 and RAW8 respectively. The video\_out port width is configured as the maximum of the individual pixel widths, and rounded to the nearest byte boundary. This results in a video\_out port width of 24.

#### Example 2: RAW7 and Four Pixels per Clock Selected in the Vivado IDE

- Single pixel width of RAW7 = 7

- Single pixel width of RAW8 = 8

With four pixels per clock selected, the effective pixels widths are 28 and 32 for RAW7 and RAW8 respectively. The <code>video\_out</code> port width is configured as the maximum of the individual pixel widths, and rounded to nearest byte boundary. This results in a <code>video\_out</code> port width of 32.

## Pixel Packing for Multiple Data Types

When multiple pixels are transferred with different pixel width, the pixels with lower width are justified to the least significant bits.

#### Example 1

When RAW12 and RAW8 are transferred with two pixels per clock, the data port width of the video\_out interface is 24 bits. Within the 24 bits the RAW8 pixels are aligned to the least significant bits as shown in the following table:

| Bit Positions | 23  | 22  | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11  | 10  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---------------|-----|-----|----|----|----|----|----|----|----|----|----|----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| RAW12         | q11 | q10 | q9 | q8 | q7 | q6 | q5 | q4 | q3 | q2 | q1 | q0 | p11 | p10 | р9 | р8 | р7 | р6 | р5 | p4 | р3 | p2 | р1 | р0 |

| RAW8          |     |     |    |    | q7 | q6 | q5 | q4 | q3 | q2 | q1 | q0 |     |     |    |    | р7 | p6 | р5 | p4 | рЗ | p2 | р1 | p0 |

#### Notes:

- 1. p0 to p11 is the 1st pixel bits of RAW12; q0 to q11 is the 2nd pixel bits of RAW12.

- 2. p0 to p7 is the 1st pixel bits of RAW8; q0 to q7 is the 2nd pixel bits of RAW8.

#### Example 2

When the core is configured with RAW6 and two pixels per clock, the video\_out port width is set to 16 bits. Within the 16 bits the RAW6 and RAW8 pixels are aligned to the least significant bits as shown in the following table:

| Bit<br>Positions | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| RAW8             | q7 | q6 | q5 | q4 | q3 | q2 | q1 | q0 | р7 | р6 | р5 | p4 | рЗ | p2 | р1 | р0 |

| RAW6             |    |    | q5 | q4 | q3 | q2 | q1 | q0 |    |    | р5 | p4 | р3 | p2 | р1 | р0 |

#### **Notes:**

- 1. p0 to p7 is the 1st pixel bits of RAW8; q0 to q7 is the 2nd pixel bits of RAW8.

- 2. p0 to p5 is the 1st pixel bits of RAW6; q0 to q5 is the 2nd pixel bits of RAW6.

## Pixel Packing for Embedded Non-Image Data Types

AXI4-Stream TDATA width is based on main data type selected from the Vivado® IDE. The position of embedded non-image data type bytes on emb\_nonimg\_tdata are listed below:

- 1st byte on emb\_nonimg\_tdata[7:0]

- 2nd byte on emb\_nonimg\_tdata[15:8] and so on.

## Pixel Packing when Video Format Bridge is not present

The width of the data port in the video\_out can be selected from Vivado IDE, under **CSI-2 Options TDATA** width. MIPI CSI-2 RX Subsystem follows the *Recommended Memory Storage* section of the MIPI CSI-2 specifications to output pixels, when a video format bridge is not present.

For more information the data type packing, refer MIPI Alliance Standard for Camera Serial Interface CSI-2 Specification [Ref 1].

#### **Example**

Pixel mapping for different data types are shown in the following table:

| Bit<br>Position | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| RAW8            | s7 | s6 | s5 | s4 | s3 | s2 | s1 | s0 | r7 | r6 | r5 | r4 | r3 | r2 | r1 | r0 | q7 | q6 | q5 | q4 | q3 | q2 | q1 | q0 | р7 | р6 | р5 | p4 | р3 | p2 | р1 | p0 |

#### Notes:

1. p0 to p7 is the 1st pixel bits of RAW8; q0 to q7 is the 2nd pixel bits of RAW8.

| Bit<br>Position | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| RAW10           | s9 | s8 | s7 | s6 | s5 | s4 | s3 | s2 | r9 | r8 | r7 | r6 | r5 | r4 | r3 | r2 | q9 | q8 | q7 | q6 | q5 | q4 | q3 | q2 | p9 | p8 | р7 | р6 | р5 | p4 | р3 | p2 |

| RAW10           | v9 | v8 | v7 | v6 | v5 | v4 | v3 | v2 | u9 | u8 | u7 | u6 | u5 | u4 | u3 | u2 | t9 | t8 | t7 | t6 | t5 | t4 | t3 | t2 | s1 | s0 | r1 | r0 | q1 | q0 | р1 | р0 |

| RAW10           | у9 | y8 | у7 | y6 | у5 | y4 | у3 | y2 | х9 | x8 | x7 | х6 | x5 | х4 | х3 | x2 | w1 | w0 | v1 | v0 | u1 | u0 | t1 | t0 | w9 | w8 | w7 | w6 | w5 | w4 | w3 | w2 |

#### Notes:

1. In RAW10, MSB 8-bits of 4 pixels are transferred first, followed by LSB 2-bits of each pixel.

| Bit<br>Position | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| RGB888          | d7 | d6 | d5 | d4 | d3 | d2 | d1 | d0 | с7 | c6 | c5 | c4 | c3 | c2 | c1 | c0 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | a7 | a6 | a5 | a4 | a3 | a2 | a1 | a0 |

| RGB888          | h7 | h6 | h5 | h4 | h3 | h2 | h1 | h0 | g7 | g6 | g5 | g4 | g3 | g2 | g1 | g0 | f7 | f6 | f5 | f4 | f3 | f2 | f1 | f0 | e7 | e6 | e5 | e4 | e3 | e2 | e1 | e0 |

#### Notes:

1. In RGB888, a0 to a7 represents the B component, b0 to b7 represents the G component and c0 to c7 represents the R component.

#### **AXI IIC**

The Camera Control Interface (CCI) of the MIPI CSI-2 specification is compatible with the fast mode variant of the I2C interface with 400 kHz operation and 7-bit slave addressing.

The AXI IIC is made available as part of this subsystem depending on user selections. See the AXI IIC Bus Interface v2.0 LogiCORE IP Product Guide (PG090) [Ref 5] for details.

# **Applications**

The Xilinx MIPI CSI-2 RX controller implements a Camera Serial Interface between a camera sensor and a programmable device performing baseband processing. Bandwidth requirement for the camera sensor interface has gone up due to the development of higher resolution cameras. Traditional parallel interfaces require an increasing number of signal lines resulting in higher power consumption. The new high speed serial interfaces, such as MIPI CSI specifications, address these expanding bandwidth requirements without sacrificing power. MIPI is a group of protocols defined by the mobile industry group to standardize all interfaces within mobile platforms such as mobile phones and tablets. However the large volumes and the economies of scale of the mobile industry is forcing other applications to also adopt these standards. As such MIPI-based camera sensors are being increasingly used in applications such as driver assistance technologies in automotive applications, video security surveillance cameras, video conferencing and emerging applications such as virtual and augmented reality.

# **Unsupported Features**

- Some YUV Data Types (YUV 420 (8-bit and 10-bit), YUV 422 10-bit) are not supported when the Video Format Bridge is included.

- · Dynamic linerate is not supported.

# **Licensing and Ordering**

## **License Checkers**

If the IP requires a license key, the key must be verified. The Vivado® design tools have several license checkpoints for gating licensed IP through the flow. If the license check succeeds, the IP can continue generation. Otherwise, generation halts with error. License checkpoints are enforced by the following tools:

- Vivado synthesis

- Vivado implementation

- write\_bitstream (Tcl command)

**IMPORTANT:** IP license level is ignored at checkpoints. The test confirms a valid license exists. It does not check IP license level.

## **License Type**

This Xilinx module is provided under the terms of the Xilinx Core License Agreement. The module is shipped as part of the Vivado® Design Suite. For full access to all core functionalities in simulation and in hardware, you must purchase a license for the core. Contact your local Xilinx sales representative for information about pricing and availability.

For more information, visit the MIPI CSI-2 RX Subsystem product web page.

Information about other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# **Product Specification**

## **Standards**

- MIPI Alliance Standard for Camera Serial Interface CSI-2 v1.1 [Ref 1]

- MIPI Alliance Physical Layer Specifications, D-PHY Specification v1.1 [Ref 6]

- Processor Interface, AXI4-Lite: see the Vivado Design Suite: AXI Reference Guide (UG1037) [Ref 7]

- Output Pixel Interface: see the AXI4-Stream Video IP and System Design Guide (UG934)

[Ref 2]

## **Resource Utilization**

For full details about performance and resource utilization, visit the Performance and Resource Utilization web page.

# **Port Descriptions**

The MIPI CSI-2 RX Subsystem I/O signals are described in Table 2-1.

Table 2-1: Port Descriptions

| Signal name                  | Direction | Description                                                                                          |

|------------------------------|-----------|------------------------------------------------------------------------------------------------------|

| lite_aclk                    | Input     | AXI clock                                                                                            |

| lite_aresetn                 | Input     | AXI reset. Active-Low                                                                                |

| S00_AXI*                     |           | AXI4-Lite interface, defined in the <i>Vivado Design Suite: AXI</i> Reference Guide (UG1037) [Ref 7] |

| dphy_clk_200M                | Input     | Clock for D-PHY core. Must be 200 MHz.                                                               |

| video_aclk                   | Input     | Subsystem clock                                                                                      |

| video_aresetn <sup>(1)</sup> | Input     | Subsystem reset. Active-Low.                                                                         |

| AXI4-Stream Video Interface  | when Vide | o Format Bridge is Present                                                                           |

Table 2-1: Port Descriptions (Cont'd)

| Signal name                | Direction    | Description                                                                                              |

|----------------------------|--------------|----------------------------------------------------------------------------------------------------------|

| video_out_tvalid           | Output       | Data valid                                                                                               |

| video_out_tready           | Input        | Slave ready to accept the data                                                                           |

|                            |              | n is based on TUSER width selected in the Vivado IDE                                                     |

|                            |              | 95-80 CRC <sup>(3)</sup>                                                                                 |

|                            |              | 79-72 ECC                                                                                                |

|                            |              | 71-70 Reserved                                                                                           |

|                            |              | 69-64 Data Type                                                                                          |

| video_out_tuser[n-1:0]     | Output       | 63-48 Word Count                                                                                         |

|                            |              | 47-32 Line Number                                                                                        |

|                            |              | 31-16 Frame Number                                                                                       |

|                            |              | 15-2 Reserved                                                                                            |

|                            |              | 1 Packet Error                                                                                           |

|                            |              | 0 Start of Frame <sup>(2)</sup>                                                                          |

| video_out_tlast            | Output       | End of line                                                                                              |

| video_out_tdata[n-1:0]     | Output       | Data n is based on Data type and number of pixels selected in the Vivado IDE (see video_out Port Width). |

|                            |              | 7-2 Data Type                                                                                            |

| video_out_tdest[7:0]       | Output       | 1-0 Virtual Channel Identifier (VC)                                                                      |

| AXI4-Stream Interface when | <br>Embedded | Non-image Interface is Selected                                                                          |

|                            |              | Data                                                                                                     |

| emb_nonimg_tdata[n-1:0]    | output       | n is based on Data type selected in the Vivado IDE (see Table 1-1).                                      |

| emb_nonimg_tdest[1:0]      | Output       | Specifies the Virtual Channel Identifier (VC) value of the embedded non-image packet                     |

| emb_nonimg_tkeep[n/8-1:0]  | Output       | Specifies valid bytes                                                                                    |

| emb_nonimg_tlast           | Output       | End of line                                                                                              |

| emb_nonimg_tready          | Input        | Slave ready to accept data                                                                               |

Table 2-1: Port Descriptions (Cont'd)

| Signal name                   | Direction  |              | Description                                 |

|-------------------------------|------------|--------------|---------------------------------------------|

|                               |            | 95-80        | CRC <sup>(3)</sup>                          |

|                               |            | 79-72        | ECC                                         |

|                               |            | 71-70        | Reserved                                    |

|                               |            | 69-64        | Data Type                                   |

|                               |            | 63-48        | Word Count                                  |

| emb_nonimg_tuser[95:0]        | Output     | 47-32        | Line Number                                 |

|                               |            | 31-16        | Frame Number                                |

|                               |            | 15-2         | Reserved                                    |

|                               |            | 1            | Packet Error                                |

|                               |            | 0            | Start of frame <sup>(2)</sup>               |

| emb_nonimg_tvalid             | Output     | Data valid   | I                                           |

| AXI4-Stream Interface when    | Video Form | nat Bridge i | s Not Present                               |

| video_out_tdata[n-1:0]        | Output     | Data         |                                             |

| video_out_tdata[ii-1.oj       | Output     | n is based   | on TDATA width selected in the Vivado IDE.  |

|                               |            | n is based   | on TDEST width selected in the Vivado IDE:  |

| video_out_tdest[n-1:0]        | Output     | 7-2          | Data type                                   |

|                               |            | 1-0          | Virtual Channel Identifier (VC)             |

| video_out_tkeep[n/8-1:0]      | Output     | Specifies    | valid bytes                                 |

| video_out_tlast               | Output     | End of lin   | е                                           |

| video_out_tready              | Input      | Slave read   | dy to accept data                           |

|                               |            | n is based   | I on TUSER width selected in the Vivado IDE |

|                               |            | 95-80        | CRC <sup>(3)</sup>                          |

|                               |            | 79-72        | ECC                                         |

|                               |            | 71-70        | Reserved                                    |

|                               |            | 69-64        | Data Type                                   |

| video_out_tuser[n-1:0]        | Output     | 63-48        | Word Count                                  |

|                               |            | 47-32        | Line Number                                 |

|                               |            | 31-16        | Frame Number                                |

|                               |            | 15-2         | Reserved                                    |

|                               |            | 1            | Packet Error                                |

|                               |            | 0            | Start of frame <sup>(2)</sup>               |

| video_out_tvalid              | Output     | Data valid   | I                                           |

|                               |            |              |                                             |

| Other Signals                 |            |              |                                             |

| Other Signals csirxss_csi_irq | Output     | Interrupt    | (active-High) from CSI-2 RX Controller      |

Table 2-1: Port Descriptions (Cont'd)

| Signal name                 | Direction      | Description                                                                                                                                                                                                                                                               |

|-----------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 Series                    |                |                                                                                                                                                                                                                                                                           |

| mipi_dphy_if                | Output         | DPHY interface                                                                                                                                                                                                                                                            |

| rxbyteclkhs                 | Output         | PPI high-speed receive byte clock                                                                                                                                                                                                                                         |

| system_rst_out              | Output         | Reset indication due to PLL reset (active-High)                                                                                                                                                                                                                           |

| dlyctrl_rdy_out             | Output         | Ready signal output from IDEALYCTRL, stating delay values are adjusted as per vtc changes                                                                                                                                                                                 |

| clk_300m                    | Input          | 300 MHz clock for IDELAYCTRL                                                                                                                                                                                                                                              |

| UltraScale+ Shared Logic    | outside Subsys | tem                                                                                                                                                                                                                                                                       |

| mipi_phy_if                 | Output         | DPHY interface                                                                                                                                                                                                                                                            |

| rxbyteclkhs                 | Output         | PPI high-speed receive byte clock                                                                                                                                                                                                                                         |

| clkoutphy_out               | Output         | PHY serial clock                                                                                                                                                                                                                                                          |

| system_rst_out              | Output         | Reset indication due to PLL reset (active-High)                                                                                                                                                                                                                           |

| pll_lock_out                | Output         | PLL lock indication (active-High)                                                                                                                                                                                                                                         |

| UltraScale+ Shared logic in | n the Subsyste | m                                                                                                                                                                                                                                                                         |

| mipi_phy_if                 | Output         | DPHY interface                                                                                                                                                                                                                                                            |

|                             |                | Inferred bitslice ports. The core infers bitslice0 of a nibble for strobe propagation within the byte group; <x> indicates byte group (0,1,2,3); <y> indicates bitslice0 position (0 for the lower nibble, 6 for the upper nibble)</y></x>                                |

| bg <x>_pin<y>_nc</y></x>    | Input          | <ul> <li>RTL Design: There is no need to drive any data on these ports.</li> <li>IP Integrator: These ports must be brought to the top level of the design to properly apply the constraints.</li> <li>Note: Pins are available only for UltraScale+ families.</li> </ul> |

| clkoutphy_in                | Input          | PHY serial clock                                                                                                                                                                                                                                                          |

| pll_lock_in                 | Input          | PLL Lock indication                                                                                                                                                                                                                                                       |

| rxbyteclkhs                 | Output         | PPI high-speed receive byte clock                                                                                                                                                                                                                                         |

#### Notes:

- 1. The active-High reset for the MIPI D-PHY core is generated internally by setting the external active-Low reset (video\_aresetn) to 0.

- 2. Each frame start packet with Virtual Channel (VC) identifier will be mapped to the first image packet and the first embedded non-image with the corresponding VC.

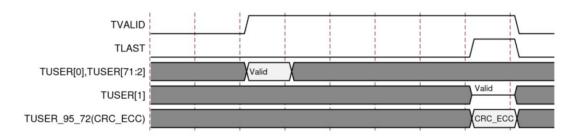

- 3. As CRC appears at the end of the MIPI packet, ECC and CRC are reported ONLY during the last beat of the stream transfer when TLAST and TVALID are asserted. You need to ignore ECC/CRC reported during other beats of the transfer. See Interface Debug for more details.

# **Register Space**

This section details registers available in the MIPI CSI-2 RX Subsystem. The address map is split into following regions:

- MIPI CSI-2 RX Controller core

- AXI IIC core

- MIPI D-PHY core

Each IP core is given an address space of 64K. Example offset addresses from the system base address when the AXI IIC and MIPI D-PHY registers are enabled are shown in Table 2-2.

Table 2-2: Sub-Core Address Offsets

| IP Cores                 | Offset                  |

|--------------------------|-------------------------|

| MIPI CSI-2 RX Controller | 0x0_0000                |

| AXI IIC                  | 0x1_0000                |

| MIPI D-PHY               | 0x2_0000 <sup>(1)</sup> |

#### Notes:

## MIPI CSI-2 RX Controller Core Registers

Table 2-3 specifies the name, address, and description of each firmware addressable register within the MIPI CSI-2 RX controller core.

Table 2-3: MIPI CSI-2 RX Controller Core Registers

| Address Offset | Register Name                       | Description                       |

|----------------|-------------------------------------|-----------------------------------|

| 0x00           | Core Configuration Register         | Core configuration options        |

| 0x04           | Protocol Configuration<br>Register  | Protocol configuration options    |

| 0x08           | Reserved <sup>(1)</sup>             |                                   |

| 0x0C           | Reserved                            |                                   |

| 0x10           | Core Status Register                | Internal status of the core       |

| 0x14           | Reserved                            |                                   |

| 0x18           | Reserved                            |                                   |

| 0x1C           | Reserved                            |                                   |

| 0x20           | Global Interrupt Enable<br>Register | Global interrupt enable registers |

| 0x24           | Interrupt Status Register           | Interrupt status register         |

<sup>1.</sup> When the AXI IIC core is not present, the MIPI D-PHY offset moves up and starts at 0x1\_0000. The software driver handles this seamlessly.

Table 2-3: MIPI CSI-2 RX Controller Core Registers (Cont'd)

| Address Offset        | Register Name                      | Description                                                       |

|-----------------------|------------------------------------|-------------------------------------------------------------------|

| 0x28                  | Interrupt Enable Register          | Interrupt enable register                                         |

| 0x2C                  | Reserved                           |                                                                   |

| 0x30                  | Generic Short Packet Register      | Short packet data                                                 |

| 0x34                  | Reserved                           |                                                                   |

| 0x38                  | Reserved                           |                                                                   |

| 0x3C                  | Clock Lane Information<br>Register | Clock lane status information                                     |

| Lane <n> Informat</n> | ion Registers                      |                                                                   |

| 0x40                  | Lane0 Information                  | Lane 0 status information                                         |

| 0x44                  | Lane1 Information                  | Lane 1 status information                                         |

| 0x48                  | Lane2 Information                  | Lane 2 status information                                         |

| 0x4C                  | Lane3 Information                  | Lane 3 status information                                         |

| 0x50                  | Reserved                           |                                                                   |

| 0x54                  | Reserved                           |                                                                   |

| 0x58                  | Reserved                           |                                                                   |

| 0x5C                  | Reserved                           |                                                                   |

| Image Information     | 1 Registers (VC0 to VC3) and I     | mage Information 2 Registers (VC0 to VC3)                         |

| 0x60                  | Image Information 1 for VC0        | Image information 1 of the current processing packet with VC of 0 |

| 0x64                  | Image Information 2 for VC0        | Image information 2 of the current processing packet with VC of 0 |

| 0x68                  | Image Information 1 for VC1        | Image information 1 of the current processing packet with VC of 1 |

| 0x6C                  | Image Information 2 for VC1        | Image information 2 of the current processing packet with VC of 1 |

| 0x70                  | Image Information 1 for VC2        | Image information 1 of the current processing packet with VC of 2 |

| 0x74                  | Image Information 2 for VC2        | Image information 2 of the current processing packet with VC of 2 |

| 0x78                  | Image Information 1 for VC3        | Image information 1 of the current processing packet with VC of 3 |

| 0x7C                  | Image Information 2 for VC3        | Image information 2 of the current processing packet with VC of 3 |

#### Notes:

- 1. Access type and reset value for all the reserved bits in the registers is read-only with value 0.

- 2. Register accesses should be word aligned and there is no support for a write strobe. WSTRB is not used internally.

- 3. Only the lower 7 bits (6:0) of the read and write address of the AXI4-Lite interface are decoded. This means that accessing address 0x00 and 0x80 results in reading the same address of 0x00.

- 4. Reads and writes to addresses outside this table do not return an error.

## **Core Configuration Register**

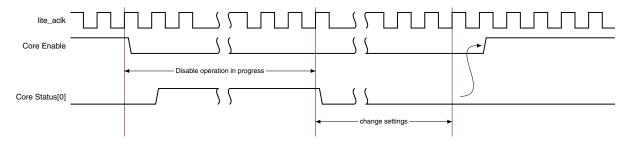

The Core Configuration register is described in Table 2-4 and allows you to enable and disable the MIPI CSI-2 RX Controller core and apply a soft reset during core operation.

Table 2-4: Core Configuration Register(0x00)

| Bits | Name        | Reset Value | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|------|-------------|-------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31–2 | Reserved    | N/A         | N/A    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 1    | Soft Reset  | 0x0         | R/W    | <ol> <li>Resets the core</li> <li>Takes core out of soft reset</li> <li>All registers reset to their default value (except for this bit, Core Enable and Active lanes configuration).</li> <li>In addition to resetting registers when this bit is set to 1:</li> <li>Shut down port is not asserted on the PPI lanes</li> <li>Internal FIFOs (PPI, Packet, Generic Short Packet) are flushed</li> <li>Control Finite State Machine (FSM) stops processing current packet. Any partially written packet to memory is marked as errored. This packet, when made available through the AXI4-Stream interface, reports the error on TUSER[1].</li> </ol> |  |

| 0    | Core Enable | 0x1         | R/W    | <ol> <li>Enables the core to receive and process packets</li> <li>Disables the core for operation</li> <li>When disabled:         <ul> <li>Shuts down port assertion on the PPI lanes</li> <li>Internal FIFOs (PPI, Packet, Generic Short Packet) are flushed</li> </ul> </li> <li>Control FSM stops processing current packet Any partially written packet to memory is marked as errored. This packet, when made available through the AXI4-Stream interface, reports the error on TUSER[1].</li> </ol>                                                                                                                                             |  |

#### **Notes:**

<sup>1.</sup> The short packet and line buffer FIFO full conditions take a few clocks to reflect in the register clock domain from the core clock domain due to Clock Domain Crossing (CDC) blocks.

## **Protocol Configuration Register**

The Protocol Configuration register is described in Table 2-5 and allows you to configure protocol specific options such as the number of lanes to be used.

Table 2-5: Protocol Configuration Register(0x04)

| Bits | Name                         | Reset Value                                       | Access              | Description                                                                             |

|------|------------------------------|---------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------|

| 31–5 | Reserved                     | N/A                                               | N/A                 | Reserved                                                                                |

| 4–3  | Maximum Lanes <sup>(1)</sup> | Number of lanes configured during core generation | R                   | Maximum lanes of the core  0x0—1 Lane 0x1—2 Lanes 0x2—3 Lanes 0x3—4 Lanes               |

| 2    | Reserved                     | N/A                                               |                     | Reserved                                                                                |

| 1–0  | Active Lanes                 | Number of lanes configured during core generation | R <sup>(2)</sup> /W | Active lanes in the core <sup>(3)</sup> 0x0—1 Lane 0x1—2 Lanes 0x2 —3 Lanes 0x3—4 Lanes |

#### Notes:

- 1. Maximum Lanes cannot exceed the number of lanes as set by the **Serial Data Lanes** parameter at generation time.

- 2. A read from this register reflects the current number of lanes being used by core. This is useful when dynamically updating the active lanes during core operation to ensure that the core is using the new active lanes information. See Chapter 3, Designing with the Subsystem for more information.

- 3. Active Lanes cannot exceed the Maximum Lanes as set in the Protocol Configuration register setting of bits 4-3.

## Core Status Register

The Core Status register is described in Table 2-6.

Table 2-6: Core Status Register(0x10)

| Bits  | Name                        | Reset Value | Access | Description                                                                           |

|-------|-----------------------------|-------------|--------|---------------------------------------------------------------------------------------|

|       |                             |             |        | Counts number of long packets written to the line buffer                              |

| 31–16 | Packet Count                | 0x0         | R      | <ul> <li>No roll-over of this counter reported/<br/>supported</li> </ul>              |

|       |                             |             |        | Count includes error packets (if any)                                                 |

| 15–4  | Reserved                    | N/A         | N/A    | N/A                                                                                   |

| 3     | Short packet FIFO Full      | 0x0         | R      | Indicates the current status of short packet FIFO full condition                      |

| 2     | Short packet FIFO not empty | 0x0         | R      | FIFO not empty: Indicates the current status of short packet FIFO not empty condition |

Table 2-6: Core Status Register(0x10) (Cont'd)

| Bits | Name                                | Reset Value | Access | Description                                                                                       |

|------|-------------------------------------|-------------|--------|---------------------------------------------------------------------------------------------------|

| 1    | Stream Line buffer Full             | 0x0         | R      | Indicates the current status of line buffer full condition                                        |

| 0    | Soft reset/Core disable in progress | 0x0         | R      | Set to 1 by the core to indicate that internal soft reset/core disable activities are in progress |

## Global Interrupt Enable Register

The Global Interrupt Enable register is described in Table 2-7.

Table 2-7: Global Interrupt Enable Register(0x20)

| Bits | Name                    | Reset Value | Access | Description                                                                                                                                                                                                                       |

|------|-------------------------|-------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–1 | Reserved                | N/A         | N/A    | Reserved                                                                                                                                                                                                                          |

| 0    | Global Interrupt enable | 0x0         | R/W    | Master enable for the device interrupt output to the system  1: Enabled—the corresponding Interrupt Enable register (IER) bits are used to generate interrupts  0: Disabled—Interrupt generation blocked irrespective of IER bits |

## Interrupt Status Register

The Interrupt Status register (ISR) is described in Table 2-8 and captures the error and status information for the core.

Table 2-8: Interrupt Status Register(0x24)

| Bits  | Name                       | Reset<br>Value | Access <sup>(1)</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|----------------------------|----------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | Frame Received             | 0x0            | R/W1C                 | Asserted when the Frame End (FE) short packet is received for the current frame                                                                                                                                                                                                                                                                                                                                                                          |

| 30–23 | Reserved                   | N/A            | N/A                   | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 22    | Word Count (WC) corruption | 0x0            | R/W1C                 | Asserted when WC field of packet header corrupted and core receives less bytes than indicated in WC field. Such a case can occur only where more than 2-bits of header are corrupted which ECC algorithm cannot report and the corruption is such that the ECC algorithm reports a higher Word Count (WC) value as part of ECC correction.  In such case core limits processing of the packet on reduced number of bytes received through PPI interface. |

Table 2-8: Interrupt Status Register(0x24) (Cont'd)

| Bits | Name                                                             | Reset<br>Value | Access <sup>(1)</sup> | Description                                                                                                                    |

|------|------------------------------------------------------------------|----------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 21   | Incorrect lane configuration                                     | 0x0            | R/W1C                 | Asserted when Active lanes is greater than Maximum lanes in the protocol configuration register                                |

| 20   | Short packet FIFO full                                           | 0x0            | R/W1C                 | Active-High signal asserted when the short packet FIFO full condition detected                                                 |

| 19   | Short packet FIFO not empty                                      | 0x0            | R/W1C                 | Active-High signal asserted when short packet FIFO not empty condition detected                                                |

| 18   | Stream line buffer full                                          | 0x0            | R/W1C                 | Asserts when the line buffer is full <sup>(2)</sup>                                                                            |

| 17   | Stop state                                                       | 0x0            | R/W1C                 | Active-High signal indicates that the lane module is currently in Stop state <sup>(3)</sup>                                    |

| 16   | Reserved                                                         | N/A            | N/A                   | N/A                                                                                                                            |

| 15   | Reserved                                                         | N/A            | N/A                   | N/A                                                                                                                            |

| 14   | Reserved                                                         | N/A            | N/A                   | N/A                                                                                                                            |

| 13   | SoT error<br>(ErrSoTHS)                                          | 0x0            | R/W1C                 | Indicates Start-of-Transmission (SoT) error detected <sup>(3)</sup>                                                            |

| 12   | SoT sync error<br>(ErrSotSyncHS)                                 | 0x0            | R/W1C                 | Indicates SoT synchronization completely failed <sup>(3)</sup>                                                                 |

| 11   | ECC 2-bit error<br>(ErrEccDouble)                                | 0x0            | R/W1C                 | Asserted when an ECC syndrome is computed and two bit errors detected in the received packet header                            |

| 10   | ECC 1-bit error<br>(Detected and Corrected)<br>(ErrEccCorrected) | 0x0            | R/W1C                 | Asserted when an ECC syndrome was computed and a single bit error in the packet header was detected and corrected              |

| 9    | CRC error<br>(ErrCrc)                                            | 0x0            | R/W1C                 | Asserted when the computed CRC code is different from the received CRC code                                                    |

| 8    | Unsupported Data Type<br>(ErrID)                                 | 0x0            | R/W1C                 | Asserted when a packet header is decoded with an unrecognized or not implemented data ID                                       |

| 7    | Frame synchronization<br>error for VC3<br>(ErrFrameSync)         | 0x0            | R/W1C                 | Asserted when an FE is not paired with a Frame Start (FS) on the same virtual channel (4)                                      |

| 6    | Frame level error for VC3<br>(ErrFrameData)                      | 0x0            | R/W1C                 | Asserted after an FE when the data payload received between FS and FE contains errors. The data payload errors are CRC errors. |

| 5    | Frame synchronization<br>error for VC2<br>(ErrFrameSync)         | 0x0            | R/W1C                 | Asserted when an FE is not paired with a FS on the same virtual channel <sup>(4)</sup>                                         |

| 4    | Frame level error for VC2<br>(ErrFrameData)                      | 0x0            | R/W1C                 | Asserted after an FE when the data payload received between FS and FE contains errors. The data payload errors are CRC errors. |

Table 2-8: Interrupt Status Register(0x24) (Cont'd)

| Bits | Name                                               | Reset<br>Value | Access <sup>(1)</sup> | Description                                                                                                                    |

|------|----------------------------------------------------|----------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 3    | Frame synchronization error for VC1 (ErrFrameSync) | 0x0            | R/W1C                 | Asserted when an FE is not paired with a FS on the same virtual channel <sup>(4)</sup>                                         |

| 2    | Frame level error for VC1<br>(ErrFrameData)        | 0x0            | R/W1C                 | Asserted after an FE when the data payload received between FS and FE contains errors. The data payload errors are CRC errors. |

| 1    | Frame synchronization error for VC0 (ErrFrameSync) | 0x0            | R/W1C                 | Asserted when a FE is not paired with a FS on the same virtual channel <sup>(4)</sup>                                          |

| 0    | Frame level error for VC0<br>(ErrFrameData)        | 0x0            | R/W1C                 | Asserted after an FE when the data payload received between FS and FE contains errors. The data payload errors are CRC errors. |

#### Notes:

- 1. W1C = Write 1 to clear.

- 2. In a line buffer full condition, reset the core using the external reset, video\_aresetn.

- 3. Reported through the PPI.

- 4. An ErrSotSyncHS error also generates this error signal.

- 5. Short packet and line buffer FIFO full conditions take a few clock periods to reflect in the register clock domain from the core clock domain due to Clock Domain Crossing (CDC) blocks.

- 6. All PPI signals captured in the ISR take a few clock periods to reflect in the register clock domain from the PPI clock domain due to CDC blocks.

- 7. Frame level errors due to ErrSotSyncHS are mapped to the recent VC processed by the ECC block of the core.

- 8. Set conditions take priority over the reset conditions for the ISR bits.

- 9. Signal names in brackets are defined in the MIPI Alliance Standard for Camera Serial Interface CSI-2 [Ref 1].

## **VC** Mapping

In the event of an ErrEccDouble error, the VC is mapped to the VC reported in the current packet header (even if corrupted).

In the event of an ErrSotSyncHS error, the VC is mapped to the previous VC processed because in this case the packet header is not available.

## Interrupt Enable Register

The Interrupt Enable register (IER) is described in Table 2-9 and allows you to selectively generate an interrupt at the output port for each error/status bit in the ISR. An IER bit set to 0 does not inhibit an error/status condition from being captured, but inhibits it from generating an interrupt.

Table 2-9: Interrupt Enable Register(0x28)

| Bits  | Name                                     | Reset Value | Access | Description                                           |

|-------|------------------------------------------|-------------|--------|-------------------------------------------------------|

| 31    | Frame Received                           | 0x0         | R/W    |                                                       |

| 30–23 | Reserved                                 | N/A         | N/A    |                                                       |

| 22    | Word Count (WC) corruption               | 0x0         | R/W    |                                                       |

| 21    | Incorrect lane configuration             | 0x0         | R/W    |                                                       |

| 20    | Short packet FIFO full                   | 0x0         | R/W    |                                                       |

| 19    | Short packet FIFO empty                  | 0x0         | R/W    |                                                       |

| 18    | Stream line buffer full                  | 0x0         | R/W    |                                                       |

| 17    | Stop state                               | 0x0         | R/W    |                                                       |

| 16    | Reserved                                 | N/A         | N/A    |                                                       |

| 15    | Reserved                                 | N/A         | N/A    | Set bits in this register to 1 to                     |

| 14    | Reserved                                 | N/A         | N/A    | generate the required                                 |

| 13    | SoT error                                | 0x0         | R/W    | interrupts. Set to 0 to disable the interrupt.        |

| 12    | SoT Sync error                           | 0x0         | R/W    | For a description of the                              |

| 11    | ECC 2-bit error                          | 0x0         | R/W    | specific interrupt you are enabling/disabling in this |

| 10    | ECC 1-bit error (Detected and Corrected) | 0x0         | R/W    | register see the ISR                                  |

| 9     | CRC error                                | 0x0         | R/W    | descriptions in Table 2-8.                            |

| 8     | Unsupported Data Type                    | 0x0         | R/W    |                                                       |

| 7     | Frame synchronization error for VC3      | 0x0         | R/W    |                                                       |

| 6     | Frame level error for VC3                | 0x0         | R/W    |                                                       |

| 5     | Frame synchronization error for VC2      | 0x0         | R/W    |                                                       |

| 4     | Frame level error for VC2                | 0x0         | R/W    |                                                       |

| 3     | Frame synchronization error for VC1      | 0x0         | R/W    |                                                       |

| 2     | Frame level error for VC1                | 0x0         | R/W    |                                                       |

| 1     | Frame synchronization error for VC0      | 0x0         | R/W    |                                                       |

| 0     | Frame level error for VC0                | 0x0         | R/W    |                                                       |

## Generic Short Packet Register

The Generic Short Packet register is described in Table 2-10. Packets received with generic short packet codes are stored in a 31-deep internal FIFO and are made available through this register. The following conditions reset the FIFO:

- External reset on video\_aresetn

- Core disable or soft reset through register settings.

Table 2-10: Generic Short Packet Register(0x30)

| Bits  | Name            | Reset Value | Access | Description               |

|-------|-----------------|-------------|--------|---------------------------|

| 31–24 | Reserved        | N/A         | N/A    | Reserved                  |

| 23–8  | Data            | 0x0         | R      | 16-bit short packet data  |

| 7–6   | Virtual Channel | 0x0         | R      | Virtual channel number    |

| 5–0   | Data Type       | 0x0         | R      | Generic short packet code |

## Clock Lane Information Register

The Clock Lane Information register is described in Table 2-11. The Stop state is captured in this register.

Table 2-11: Clock Lane Information Register(0x3C)

| Bits | Name       | Reset Value | Access | Description              |

|------|------------|-------------|--------|--------------------------|

| 31–2 | Reserved   | N/A         | N/A    | Reserved                 |

| 1    | Stop state | 0x0         | R      | Stop state on clock lane |

| 0    | Reserved   | N/A         | N/A    | Reserved                 |

## Lane<n> Information Registers

The Lane<n> Information register, where n is 0, 1, 2 or 3, is described in Table 2-12 and provides the status of the <n> data lane. This register is reset when any write to the Protocol Configuration register is detected, irrespective of whether the Protocol Configuration register contents are updated or not.

Table 2-12: Lane 0, 1, 2, 3 Information Register(0x40, 0x44, 0x48, 0x4C)

| Bits | Name       | Reset Value | Access | Description <sup>(2)</sup>                                                                                 |

|------|------------|-------------|--------|------------------------------------------------------------------------------------------------------------|

| 31–6 | Reserved   | N/A         | N/A    | Reserved                                                                                                   |

| 5    | Stop state | 0x0         | R      | Detection of Stop state<br>Active-High signal indicates that the lane<br>module is currently in stop state |

| 4    | Reserved   | N/A         | N/A    | Reserved                                                                                                   |

| 3    | Reserved   | N/A         | N/A    | Reserved                                                                                                   |

| 2    | Reserved   | N/A         | N/A    | Reserved                                                                                                   |

Table 2-12: Lane 0, 1, 2, 3 Information Register(0x40, 0x44, 0x48, 0x4C) (Cont'd)

| Bits | Name           | Reset Value | Access | Description <sup>(2)</sup>                                                                      |

|------|----------------|-------------|--------|-------------------------------------------------------------------------------------------------|

| 1    | SoT error      | 0x0         | R      | Detection of SoT Error (ErrSotHS)<br>Indicates SoT error detected                               |

| 0    | SoT Sync error | 0x0         | R      | Detection of SoT Synchronization Error (ErrSotSyncHS) Indicates that SoT synchronization failed |

#### **Notes:**

- 1. Lane Information registers are present only for the maximum defined number of lanes. Reads to others registers gives 0x0.

- 2. All bits are reported through the PPI.

## Image Information 1 Registers (VC0 to VC3)

The Image Information 1 registers are described in Table 2-13 and provide image information for line count and byte count per VC. The byte count gets updated whenever a long packet (from Data Types 0x18 and above) for the corresponding virtual channel is processed by the control FSM. The line count is updated whenever the packet is written into the line buffer.

Table 2-13: Image Information 1 Registers(0x60, 0x68, 0x70, 0x78)

| Bits  | Name       | Reset Value | Access | Description                                                     |

|-------|------------|-------------|--------|-----------------------------------------------------------------|

| 31–16 | Line count | 0x0         | R      | Number of long packets written to line buffer                   |

| 15–0  | Byte count | 0x0         | R      | Byte count of current packet being processed by the control FSM |

## Image Information 2 Registers (VC0 to VC3)

The Image Information 2 registers are described in Table 2-14 and provide the image information Data Type. The Data Type is updated whenever a long packet (Data Types 0x18 and above) for the corresponding virtual channel is processed by the control FSM.

Table 2-14: Image Information 2 Registers(0x64, 0x6C, 0x74, 0x7C)

| Bits | Name      | Reset Value | Access | Description                                                |

|------|-----------|-------------|--------|------------------------------------------------------------|

| 31–6 | Reserved  | N/A         | N/A    | Reserved                                                   |

| 5–0  | Data Type | 0x0         | R      | Data Type of current packet being processed by control FSM |

## **AXI IIC Registers**

The AXI IIC registers are available when **Include IIC** is selected in the Vivado IDE. For details about AXI IIC registers, see the AXI IIC Bus Interface v2.0 LogiCORE IP Product Guide (PG090) [Ref 5].

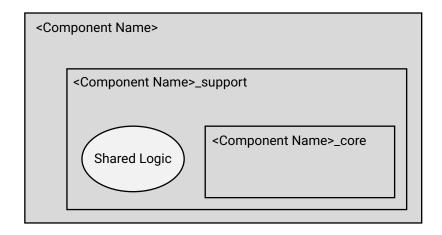

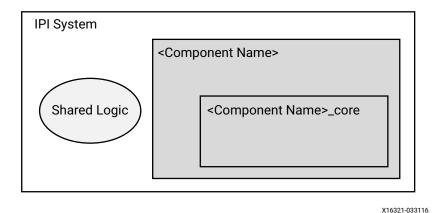

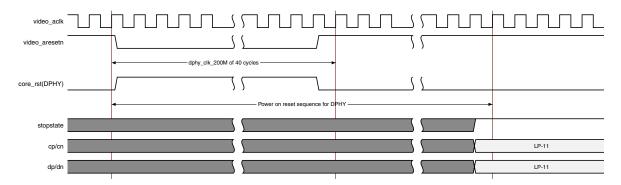

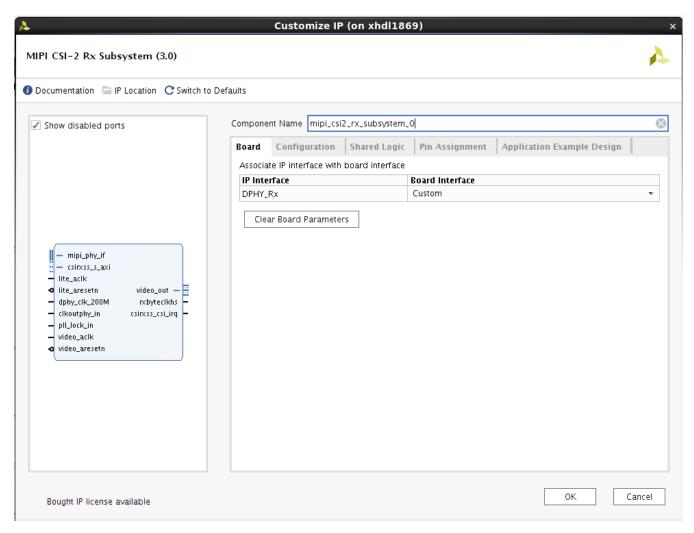

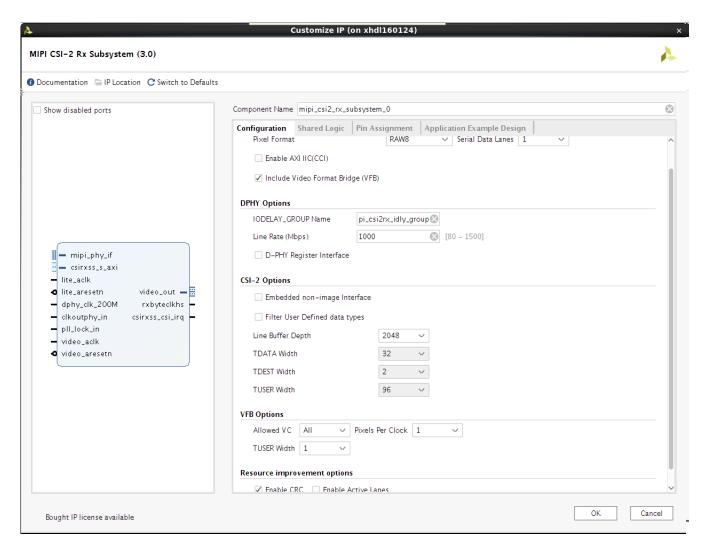

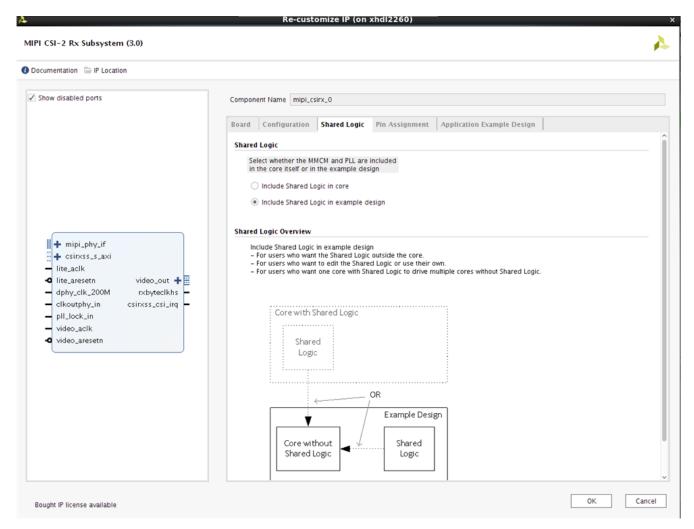

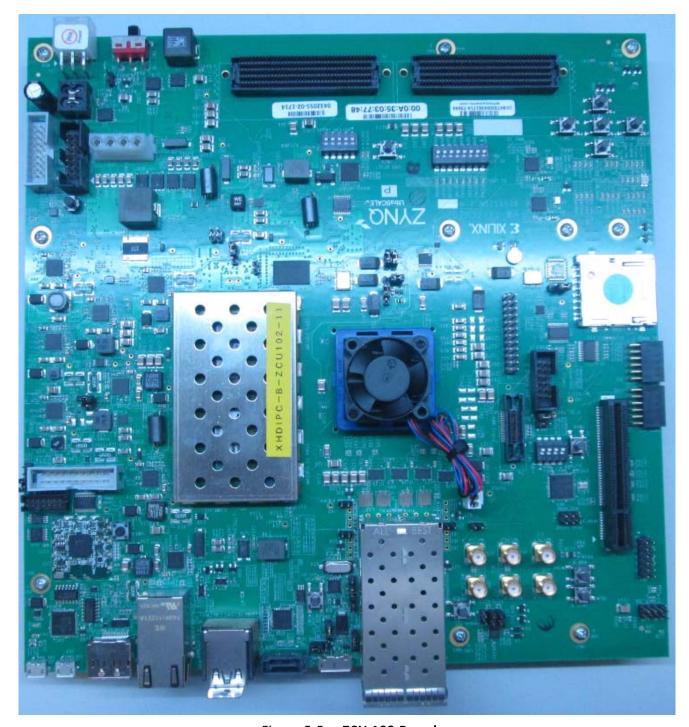

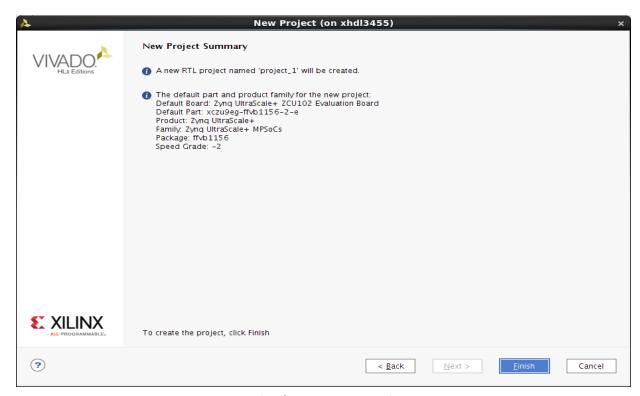

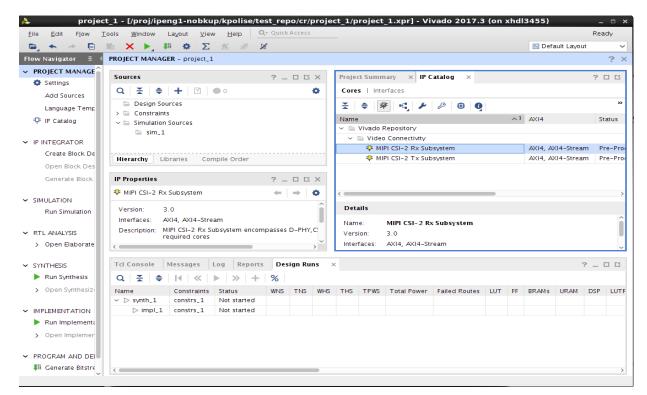

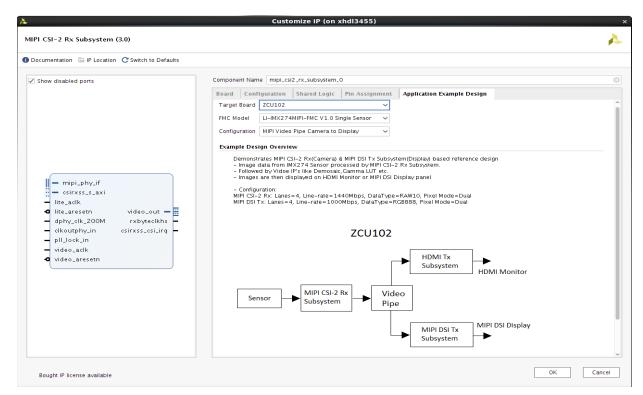

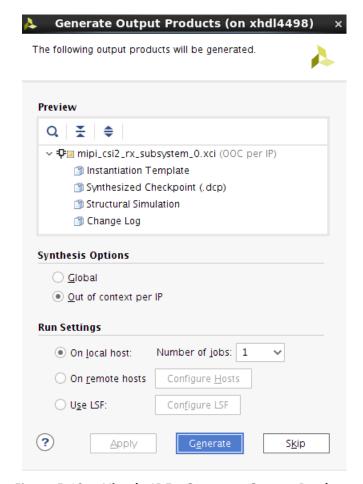

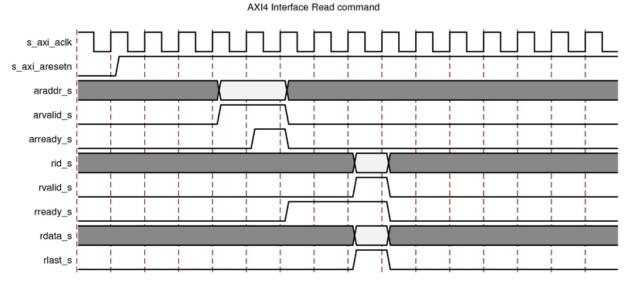

## **MIPI D-PHY Registers**