# AXI High Bandwidth Memory Controller v1.0

# LogiCORE IP Product Guide

Vivado Design Suite

PG276 (v1.0) November 2, 2022

Xilinx is creating an environment where employees, customers, and partners feel welcome and included. To that end, we're removing noninclusive language from our products and related collateral. We've launched an internal initiative to remove language that could exclude people or reinforce historical biases, including terms embedded in our software and IPs. You may still find examples of non-inclusive language in our older products as we work to make these changes and align with evolving industry standards. Follow this <u>link</u> for more information.

# Table of Contents

| Chapter 1: Introduction                                                    | 4    |

|----------------------------------------------------------------------------|------|

| Features                                                                   |      |

| IP Facts                                                                   |      |

| Chapter 2: Overview                                                        | 7    |

| Core Overview                                                              | 7    |

| Navigating Content by Design Process                                       | 8    |

| Unsupported Features                                                       | 8    |

| Licensing and Ordering                                                     | 9    |

| Chapter 3: Product Specification                                           | . 10 |

| Standards                                                                  | . 10 |

| Performance                                                                | . 11 |

| Lateral AXI Switch Access Throughput Loss                                  | . 12 |

| Resource Use                                                               | . 15 |

| Port Descriptions                                                          | 16   |

| Data Path Error Protection                                                 | 20   |

| Chapter 4: Designing with the Core                                         | . 21 |

| Clocking                                                                   | . 21 |

| HBM Performance Concepts                                                   | . 22 |

| Non-Synthesizable Traffic Generator Considerations for Workload Simulation | 31   |

| Chapter 5: Design Flow Steps                                               | 35   |

| Customizing and Generating the Core                                        | . 35 |

| Constraining the Core                                                      | 47   |

| Simulation                                                                 | . 48 |

| Synthesis and Implementation                                               | 48   |

| Chapter 6: Example Design                                                  | . 49 |

| Implementing the Example Design                                            | . 49 |

| Simulating the Example Design                                              | . 52 |

| Non-Synthesizable Traffic Generator<br>Synthesizable Traffic Generator                                                          |                             |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Appendix A: Upgrading                                                                                                           | 71                          |

| Appendix B: Debugging<br>Hardware Manager - HBM Debug Interface                                                                 |                             |

| Finding Help on Xilinx.com<br>Debug Tools                                                                                       | 83                          |

| 5                                                                                                                               |                             |

| Appendix C: Memory Controller Register Map                                                                                      | 86                          |

| Appendix C: Memory Controller Register Map<br>Appendix D: Additional Resources and Legal Notices                                |                             |

|                                                                                                                                 | 92                          |

| Appendix D: Additional Resources and Legal Notices<br>Xilinx Resources<br>Documentation Navigator and Design Hubs               | <b>92</b><br>92<br>92       |

| Appendix D: Additional Resources and Legal Notices<br>Xilinx Resources<br>Documentation Navigator and Design Hubs<br>References | <b>92</b><br>92<br>92<br>92 |

| Appendix D: Additional Resources and Legal Notices<br>Xilinx Resources<br>Documentation Navigator and Design Hubs               |                             |

# AMDA XILINX

# Chapter 1

# Introduction

The AXI High Bandwidth Memory Controller (HBM) is an integrated IP core. This core provides access to a HBM stack with up to 16 AXI3 slave ports, each with its own independent clocking. The AXI HBM solution interfaces with JEDEC JESD235 HBM2 GEN2 memory devices. A small soft IP block is generated to configure and initialize the HBM IP as well as provide debug access in the Vivado<sup>®</sup> Hardware Manager. The IP has a configurable user interface available through the Vivado IP Catalog.

## Features

- User access to the HBM stacks through AXI3 slave ports

- 。 16 independent 256-bit ports

- 。 Optional 32-bit data bus extension

- Can be used for either user parity protection or data width extension

- 。 64 AXI IDs support per port

- 16 x 16 AXI crossbar switch per HBM stack

- Full memory space access from all AXI ports

- Up to 128 Gb (16 GB) directly addressable data storage in two stack configuration

- Expansion to 32 AXI ports for dual stack configurations

- AMBA® APB 32-bit register bus access

- $_{\circ}$   $\,$  Vivado  $^{\mbox{\scriptsize R}}$  generated initialization with optional user access port

- Memory performance

- 。 Configurable access reordering to improve bandwidth utilization

- Reordering transactions with different IDs

- Honors ordering rules within IDs

- Read after Write and Write after Write coherency checking for transactions generated by same master with same ID

Send Feedback

- Refresh cycles are handled by the controller

- Temperature controlled refresh rates

- Optional hidden single row refresh option to minimize overhead

- Increase efficiency based on user access patterns

- Flexible memory address mapping from AXI to the physical HBM stacks

- Configurable reordering and memory controller behaviors to optimize latency or bandwidth

- Grouping of Read/Write operations

- Minimizing page opening activation overhead

- Performance monitoring and logging activity registers

- Bandwidth measured at each HBM memory controller

- Configurable sample duration

- Maximum, minimum, and average Read and Write bandwidth is logged

- Reliability (RAS) support

- Optional SECDED ECC

- Partial word writes supported with Read Modify Write (RMW) operation

- Background scan of memory for error scrubbing

- Correctable ECC errors found are fixed and updated in memory

- Optional parity with memory access retry due to data parity errors in Write operations

- Parity data protection available in datapath between user logic and HBM

- The external parity uses the 32-bit WDATA\_PARITY and RDATA\_PARITY buses with one parity bit per byte of data.

- Uses Odd parity where a 1 is asserted for every data byte when the sum of the bits in the byte is an odd value.

- Error logging registers

- Power management

- Per memory channel clock gating

- Per memory channel divided clock rate for reduced power

- Power down mode supported

- Optional self-refresh mode to retain contents of memory

- Selectable idle timeout to self-refresh entry

- JEDEC JESD235 HBM2 GEN2 memory stack organization

- <sup>o</sup> 32 Gb density (4H stack), 64 Gb density (8H stack) depending on the device

- 16 independent 64-bit channels

- Optional PHY only interface

# **IP Facts**

| LogiCORE IP Facts Table                                                                       |                                                                                                                                                                                                                           |  |  |  |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Core Specifics                                                                                |                                                                                                                                                                                                                           |  |  |  |

| Supported Device Family <sup>1</sup> Virtex <sup>®</sup> UltraScale+ <sup>™</sup> HBM Devices |                                                                                                                                                                                                                           |  |  |  |

| Supported User Interfaces                                                                     | AXI3, AMBA APB                                                                                                                                                                                                            |  |  |  |

| Resources                                                                                     | N/A                                                                                                                                                                                                                       |  |  |  |

|                                                                                               | Provided with Core                                                                                                                                                                                                        |  |  |  |

| Design Files                                                                                  | Encrypted RTL                                                                                                                                                                                                             |  |  |  |

| Example Design                                                                                | Verilog                                                                                                                                                                                                                   |  |  |  |

| Test Bench                                                                                    | Verilog AXI Traffic Generator                                                                                                                                                                                             |  |  |  |

| Constraints File                                                                              | Provided                                                                                                                                                                                                                  |  |  |  |

| Simulation Model                                                                              | Encrypted Verilog                                                                                                                                                                                                         |  |  |  |

| Supported S/W Driver                                                                          | N/A                                                                                                                                                                                                                       |  |  |  |

| Tested Design Flows <sup>2</sup>                                                              |                                                                                                                                                                                                                           |  |  |  |

| Design Entry                                                                                  | Vivado® Design Suite                                                                                                                                                                                                      |  |  |  |

| Simulation <sup>(3)(4)</sup>                                                                  | Simulation is supported with Verilog Compliler Simulator (VCS), Incisive<br>Enterprise Simulator (IES), and Questa Advanced Simulator. For supported<br>simulator versions, see Xilinx Design Tools: Release Notes Guide. |  |  |  |

| Synthesis                                                                                     | Vivado Synthesis                                                                                                                                                                                                          |  |  |  |

| Support                                                                                       |                                                                                                                                                                                                                           |  |  |  |

| Release Notes and Known Issues                                                                | Master Answer Record: 69267                                                                                                                                                                                               |  |  |  |

| All Vivado IP Change Logs                                                                     | Master Vivado IP Change Logs: 72775                                                                                                                                                                                       |  |  |  |

| Pr                                                                                            | ovided by Xilinx® at the Xilinx Support web page                                                                                                                                                                          |  |  |  |

#### Notes:

1. For a complete list of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

- 3. Behavioral simulations using verilog simulation models are supported. Netlist (post-synthesis and post-implementation) simulations are not supported.

- 4. Simulations in 32-bit environments are not recommended due to the limitation of addressable system memory.

# Chapter 2

# AMDA XILINX

# Overview

# **Core Overview**

The AXI High Bandwidth Memory Controller provides access to one or both the 1024-bit wide HBM stacks depending on the selected device; 64 Gb for 4H devices or 128 Gb for 8H devices. Each stack is split into eight independent memory channels, each of which is further divided into two 64-bit pseudo channels. Pseudo channel memory access is limited to its own section of the memory (1/16 of the stack capacity). Furthermore, each memory channel can operate at an independent clock rate that is an integer divide of a global reference clock.

The AXI HBM Controller has simplified the interface between HBM and CLB-based user logic in several ways. The AXI3 protocol is selected to provide a proven standardized interface. The 16 AXI ports provided match the total throughput of the HBM. Each port operates at a 4:1 ratio to lower the clock rate required in the user logic. This ratio requires a port width of 256-bits ( $4 \times 64$ ). Each AXI3 channel has 6-bit AXI ID port which helps in reordering transactions to achieve the required bandwidth. On the selected AXI3 channel, if the transactions are triggered using a different ID tag, then the transactions are triggered using same ID tag, then the transactions are triggered.

The ports are distributed across the general interconnect to reduce congestion and each port is based on an independent clock domain. This flexibility, along with each AXI port attached to its own registered column interface, reduces congestion and eases timing closure.

The 16 × 16 AXI crossbar switch is included in this core which allows each memory port to access the full HBM space by addressing all 16 pseudo channels. In the case of a two-stack system, this is extended to a 32 × 32 crossbar to allow direct access across both HBM stacks as shown in the following 4H device figure.

| + + + + + + + + + + + + + + + + + + + | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |   |

|---------------------------------------|-------------------------------------------------------|---|

| 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | ; |

#### Figure 1: HBM Two Stack Configuration

## **Navigating Content by Design Process**

Xilinx<sup>®</sup> documentation is organized around a set of standard design processes to help you find relevant content for your current development task. All Versal<sup>®</sup> ACAP design process Design Hubs and the Design Flow Assistant materials can be found on the Xilinx.com website. This document covers the following design processes:

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, functional simulation, and evaluating the Vivado<sup>®</sup> timing, resource use, and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Port Descriptions

- Clocking

## **Unsupported Features**

The following features are not supported in the AXI3 interface or the HBM IP:

- Fixed addressing mode

- QoS signaling

- HBM GEN1 Legacy operating mode

# **Licensing and Ordering**

This Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP module is provided at no additional cost with the Xilinx Vivado<sup>®</sup> Design Suite under the terms of the Xilinx End User License.

*Note*: To verify that you need a license, check the License column of the IP Catalog. Included means that a license is included with the Vivado<sup>®</sup> Design Suite; Purchase means that you have to purchase a license to use the core.

For more information about this core, visit the HBM enabled Virtex<sup>®</sup> UltraScale+<sup>™</sup> device product page.

Information about other Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# Chapter 3

# **Product Specification**

The AXI High Bandwidth Memory Controller provides user logic access to the attached HBM through the AXI3 ports distributed throughout the general interconnect. Each of the 16 AXI3 ports per stack has a throughput capacity equal to 1/16 of the total HBM bandwidth.

Each of these ports has pipeline registers to facilitate timing closure and routing of user logic. Each port can optionally address the entire HBM space (global addressing) to greatly reduce the need for any cross channel routing in general interconnect. Alternatively, non-global addressing (direct addressing) limits an AXI3 port to the associated pseudo channel with the least latency.

The eight memory controllers in a stack each have flexibility to optimize latency and utilization trade-offs for a given application by using different reordering or operating modes. Also, activity monitoring registers are provided to facilitate analysis.

Reliability is enhanced with full datapath parity checking and optional SECDED ECC protection in memory. Error logging is provided by ECC status registers.

## Standards

The AXI HBM controller supports AXI3. For more information of features not included, see the Unsupported Features.

Documented registers are addressable through the AMBA APB bus protocol.

## Performance

#### **Maximum Frequencies**

The following table shows the maximum frequencies for the AXI HBM controller.

#### Table 1: Maximum Frequencies

| Clock                       | Maximum Frequency <sup>1</sup> (MHz) | Notes           |

|-----------------------------|--------------------------------------|-----------------|

| AXI3 Port Clocks[15:0]      | 450                                  | Per AXI3 port   |

| AMBA APB Register Bus Clock | 100                                  |                 |

| Memory CLK[7:0]             | 900                                  | Per HBM channel |

Notes:

1. Maximum frequency supported for fastest speed grade.

#### Latency

The following table shows the latency for the AXI HBM controller.

#### Table 2: Latency

| Latency Component<br>Description                 | Open Page – No<br>Activate | Closed Page – Activate | Notes                                                                  |

|--------------------------------------------------|----------------------------|------------------------|------------------------------------------------------------------------|

| Description                                      | Memory Clocks              | Memory Clocks          |                                                                        |

| AXI Port Latency – Global<br>addressing disabled | 90                         | 108                    | Direct routing from AXI3 port to aligned Memory Channel <sup>1</sup> . |

| AXI Port Latency – Global<br>addressing enabled  | 110 (Minimum)              |                        |                                                                        |

Notes:

1. For more information, see Table 6: AXI Port Assignments in the Port Descriptions section.

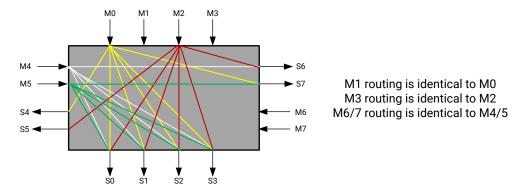

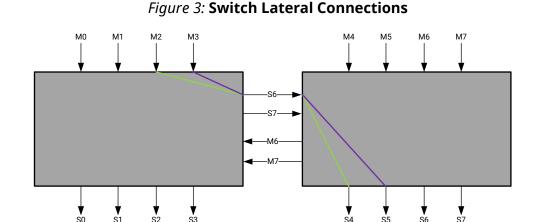

# Lateral AXI Switch Access Throughput Loss

Two lateral connections are provided between sets of 4 masters x 4 slaves within the switch, with one lateral connected to M0 and M1, and the other connected to M2 and M3. The shared connections limit the maximum throughput laterally to 50% of the full bandwidth, but enables global addressing from any AXI port to any portion of the HBM. For Write cycles there is a single dead cycle when switching between masters on the lateral channel. The throughput loss due to this inserted cycle depends on the block size of the writes and the extent to which throughput is switch limited, rather than HBM MC limited.

For East/West transactions within an AXI Switch instance there is no lateral performance loss. For East/West transactions which leave an AXI Switch instance there *will* be a lateral throughput performance loss.

A transaction that is stalled by the AXI Master while crossing switches will continue to reserve the lateral path, preventing its use from other channels. For example, an AXI port, reading from a memory location that requires crossing switches, is unable to receive a full data burst and deasserts RREADY mid-transaction. This would cause the lateral path to remain claimed by this transaction and unable to process transactions from other AXI channels that require the same path.

A similar behavior may occur on a write transaction. When a write command is issued and accepted by the switch, the corresponding data path is reserved and will continue to be held until the data has been fully transmitted. The AXI protocol allows commands to be sent first and data at a later time. However, doing that can result in significant impact to overall switch performance if the data path is a lateral connection needed by another command. It is recommended that write commands are only sent when the corresponding write data is available.

X22063-072320

| MC Transaction                      | Performance Impact |

|-------------------------------------|--------------------|

| M0/1 going east to S2/S3            | No                 |

| M0/1 going west to S4 or east to S7 | Yes                |

| M2/3 going west to S0/S1            | No                 |

| M2/3 going east to S6 or west to S5 | Yes                |

### Table 3: MC Performance Impact Per Switch Instance

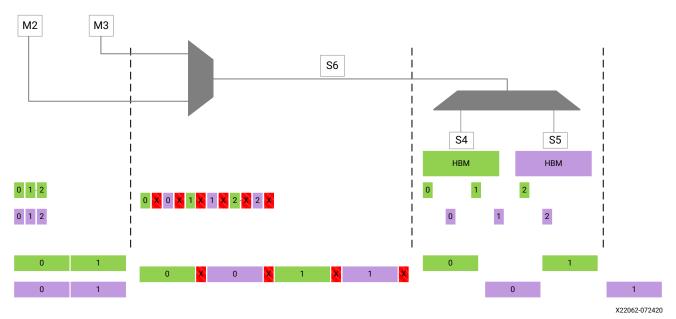

A Write sequence with near 100% MC throughput results in the largest drop in throughput due to the extra switching cycle. As a result, smaller blocks have a larger percentage loss than larger blocks. The following figure demonstrates the lateral throughput loss with 32-byte and 256-byte transactions. For the 32-byte transactions two masters are each issuing three 32-byte bursts which must laterally traverse the AXI switch. For the 256-byte transactions each master is issuing two 256-byte bursts which must laterally traverse the AXI switch. In the 32-byte case there is one clock inserted between each data burst for each master which results in a total of 12 clock cycles to move 6 beats of data. In the 256-byte case there is one idle clock inserted between each 256-byte burst which results in a total of 36 clock cycles to move 32 beats of data. Because M2 and M3 only have access to one lateral slave port, the total bandwidth for these ports is split between the two masters. This results in a total efficiency for the 32-byte transactions of about 25% due to the additional clock cycles for switching between masters as well as both masters sharing a single slave port. For the 256-byte transactions these same behaviors result in approximately 44.4% efficiency.

### AMDZI XILINX

#### Figure 4: Switch Throughput Pattern

# *Table 4:* Measured Lateral Throughput Efficiency Based on 100% Page Hit Rate Write Streams for 4H Stack

| Block Size | Switch Limited BW Pct |

|------------|-----------------------|

| 32 B       | 24.9%                 |

| 64 B       | 33.3%                 |

| 128 B      | 39.9%                 |

| 256 B      | 44.4%                 |

| 512 B      | 47%                   |

# **Resource Use**

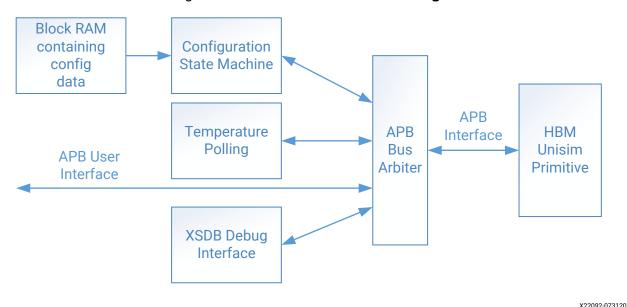

Minimal CLB and block RAM resources are required to support the HBM stack controller. Primarily the logic is used for register initialization based on the values set in the Vivado<sup>®</sup> HBM wizard. Additional CLB resources are used for the clocks required for the design, the enabled AXI interface(s), and the APB register interface. The following figure shows the HBM controller initialization logic.

# **Port Descriptions**

The following table shows the AXI HBM controller signals.

#### Table 5: AXI HBM Controller Signals<sup>1</sup>

| Port Name           | I/O | Description                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AXI_xx_ACLK         | I   | Clock for the AXI Interface                                                                                                                                                                                                                                                                                                                                      |

| AXI_xx_ARESET_N     | I   | Active-Low AXI Reset. This reset port should only be used prior to the start of data traffic. Using it after traffic has begun will cause the AXI interface and the memory controller to become out-of-sync.<br>When the switch is enabled, the IP will internally connect all of the AXI_xx_ARESET_N pins together because the memory behaves as a single unit. |

| AXI xx ARADDR       | I   | [32:0] Read Address for 4H Stack, [33:0] Read Address for 8H Stack <sup>2</sup>                                                                                                                                                                                                                                                                                  |

| <br>AXI_xx_ARBURST  | I   | [1:0] Address Read Burst. The fixed address burst type (2'b00) is not supported                                                                                                                                                                                                                                                                                  |

| AXI_xx_ARID         | I   | [5:0] Read Address ID Tag                                                                                                                                                                                                                                                                                                                                        |

| AXI_xx_ARLEN        | I   | [3:0] Read Burst Length                                                                                                                                                                                                                                                                                                                                          |

| AXI_xx_ARSIZE       | I   | [2:0] Read Burst Size<br>Only 256-bit size supported (3'b101)                                                                                                                                                                                                                                                                                                    |

| AXI_xx_ARVALID      | I   | Read Address Valid                                                                                                                                                                                                                                                                                                                                               |

| AXI_xx_ARREADY      | 0   | Read address Ready                                                                                                                                                                                                                                                                                                                                               |

| AXI_xx_AWADDR       | I   | [32:0] Write Address for 4H Stack, [33:0] Write Address for 8H Stack <sup>2</sup>                                                                                                                                                                                                                                                                                |

| AXI_xx_AWBURST      | I   | [1:0] Write Burst Type. The fixed address burst type (2'b00) is not supported.                                                                                                                                                                                                                                                                                   |

| AXI_xx_AWID         | I   | [5:0] Write Address ID                                                                                                                                                                                                                                                                                                                                           |

| AXI_xx_AWLEN        | I   | [3:0] Write Burst Length                                                                                                                                                                                                                                                                                                                                         |

| AXI_xx_AWSIZE       | I   | [2:0] Write Burst<br>Only 256-bit size supported (3'b101)                                                                                                                                                                                                                                                                                                        |

| AXI_xx_AWVALID      | I   | Write Address Valid                                                                                                                                                                                                                                                                                                                                              |

| AXI_xx_RREADY       | I   | Read Ready                                                                                                                                                                                                                                                                                                                                                       |

| AXI_xx_BREADY       | I   | Response Ready                                                                                                                                                                                                                                                                                                                                                   |

| AXI_xx_WDATA        | I   | [255:0] Write Data                                                                                                                                                                                                                                                                                                                                               |

| AXI_xx_WLAST        | I   | Write Last                                                                                                                                                                                                                                                                                                                                                       |

| AXI_xx_WSTRB        | I   | [31:0] Write Strobe                                                                                                                                                                                                                                                                                                                                              |

| AXI_xx_WDATA_PARITY | I   | [31:0] Write Data<br>Can be used for user parity or data width expansion. User parity is calculated on a<br>per byte basis and the calculation is Odd. For Odd parity a 1 is asserted per byte if<br>the sum of the bits in that byte is Odd.                                                                                                                    |

| AXI_xx_WVALID       | I   | Write Valid                                                                                                                                                                                                                                                                                                                                                      |

| AXI_xx_AWREADY      | 0   | Write Address Ready                                                                                                                                                                                                                                                                                                                                              |

| AXI_xx_RDATA_PARITY | 0   | [31:0] Read Data Parity<br>Can be used for user parity or data width expansion. User parity is calculated on a<br>per byte basis and the calculation is Odd. For Odd parity a 1 is asserted per byte if<br>the sum of the bits in that byte is Odd.                                                                                                              |

| AXI_xx_RDATA        | 0   | [255:0] Read Data                                                                                                                                                                                                                                                                                                                                                |

| AXI_xx_RID          | 0   | [5:0] Read ID Tag                                                                                                                                                                                                                                                                                                                                                |

#### Table 5: AXI HBM Controller Signals<sup>1</sup> (cont'd)

| Port Name           | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|---------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AXI_xx_RLAST        | 0   | Read Last                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| AXI_xx_RRESP        | 0   | I:0] Read Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| AXI_xx_RVALID       | 0   | Read Valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| AXI_xx_WREADY       | 0   | Write Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| AXI_xx_BID          | 0   | [5:0] Response ID Tag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| AXI_xx_BRESP        | 0   | [1:0] Write Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| AXI_xx_BVALID       | 0   | Write Response Valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| APB_y_PCLK          | Ι   | APB Port Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| APB_y_PENABLE       | Ι   | APB Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| APB_y_PRESET_N      | I   | APB active-Low Reset. When this bit is asserted, it resets the entire memory interface including the controller, PHY, and memory stacks. Runs in the APB_PCLK domain and can be asserted/deasserted asynchronously with a minimum pulse width of one APB clock cycle.                                                                                                                                                                                                                                                                                                                              |  |  |

| APB_y_PSEL          | Ι   | APB Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| APB_y_PWRITE        | Ι   | APB Bus Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| APB_y_PRDATA        | 0   | [31:0] APB Read Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| APB_y_PREADY        | 0   | APB Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| APB_y_PSLVERR       | 0   | APB Transfer Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| DRAM_y_STAT_CATTRIP | 0   | HBM Catastrophic Temperature Flag. This bit is asserted when a DRAM's temperature has exceeded 120C. When this bit is asserted, ensure to immediately disable the memory access.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| DRAM_y_STAT_TEMP    | 0   | [6:0] Temperature in Celsius. This is the worst-case scenario for the two memory stacks. When the temperature of the two memory stacks is over 5°C, the highest temperature of the two is driven out on both the DRAM_y_STAT_TEMP ports. When the temperature of the two memory stacks is below 5°C, the lowest temperature of the two stacks is driven out on both the DRAM_y_STAT_TEMP ports. The update frequency is configurable. When there are two ports in the IP for a two Stack enabled design, the data on both ports is identical because it is driven by a single source. <sup>3</sup> |  |  |

| apb_complete_0      | 0   | Indicates initial configuration sequence for Stack-0 is complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| apb_complete_1      | 0   | Indicates initial configuration sequence for Stack-1 is complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

#### Notes:

- 1. There are two AXI ports per memory controller enabled and one APB port per memory stack enabled.

- 2. In  $AXI_XX_ARADDR$  and  $AXI_XX_AWADDR$  signals:

- a. 4H Stack Bit [32], 8H Stack[33] is used to select the HBM Stack.

- b. 4H Stack Bits [31:28], 8H Stack[32:29] are used to select the AXI Port.

- c. 4H Stack Bits [27:5], 8H Stack[28:5] are used to access the actual HBM.

- d. Bits [4:0] are unused because the AXI\_XX\_ARSIZE and AXI\_\_XX\_AWSIZE signals are always 3'b101 (32-byte aligned).

- 3. This behavior change is implemented in the Vivado<sup>®</sup> Design Suite from 2018.3 release. Prior to 2018.3, lower 3-bits represented the refresh rate required for the memory based on the stack temperature.

The following table shows the AXI port assignments in the general interconnect. This includes the start address associated with each HBM channel, memory controller, and pseudo channel to which it is aligned. In non-global address mode, an AXI port can only access its associated pseudo channel. Each AXI port has a fixed address map of 2 Gb (4H Stack) or 4 Gb (8H Stack). Therefore in non-global address mode each AXI port must be mapped to the address space with its start address mentioned in the first column and ending before the start address of the next pseudo channel. In global address mode each port can access all pseudo channels but with varying performance and latency.

| Start Address<br>(16 GB) | Start Address<br>(8 GB) | HBM Stack | AXI Port | HBM Channel/PC | HBM Controller |

|--------------------------|-------------------------|-----------|----------|----------------|----------------|

| 0x0_0000_0000            | 0x0_0000_0000           | Left      | 0        | A/PC0          | MC0            |

| 0x0_2000_0000            | 0x0_1000_0000           | Left      | 1        | A/PC1          | MC0            |

| 0x0_4000_0000            | 0x0_2000_0000           | Left      | 2        | E/PC0          | MC1            |

| 0x0_6000_0000            | 0x0_3000_0000           | Left      | 3        | E/PC1          | MC1            |

| 0x0_8000_0000            | 0x0_4000_0000           | Left      | 4        | B/PC0          | MC2            |

| 0x0_A000_0000            | 0x0_5000_0000           | Left      | 5        | B/PC1          | MC2            |

| 0x0_C000_0000            | 0x0_6000_0000           | Left      | 6        | F/PC0          | MC3            |

| 0x0_E000_0000            | 0x0_7000_0000           | Left      | 7        | F/PC1          | MC3            |

| 0x1_0000_0000            | 0x0_8000_0000           | Left      | 8        | C/PC0          | MC4            |

| 0x1_2000_0000            | 0x0_9000_0000           | Left      | 9        | C/PC1          | MC4            |

| 0x1_4000_0000            | 0x0_A000_0000           | Left      | 10       | G/PC0          | MC5            |

| 0x1_6000_0000            | 0x0_B000_0000           | Left      | 11       | G/PC1          | MC5            |

| 0x1_8000_0000            | 0x0_C000_0000           | Left      | 12       | D/PC0          | MC6            |

| 0x1_A000_0000            | 0x0_D000_0000           | Left      | 13       | D/PC1          | MC6            |

| 0x1_C000_0000            | 0x0_E000_0000           | Left      | 14       | H/PC0          | MC7            |

| 0x1_E000_0000            | 0x0_F000_0000           | Left      | 15       | H/PC1          | MC7            |

| 0x2_0000_0000            | 0x1_0000_0000           | Right     | 16       | A/PC0          | MC8            |

| 0x2_2000_0000            | 0x1_1000_0000           | Right     | 17       | A/PC1          | MC8            |

| 0x2_4000_0000            | 0x1_2000_0000           | Right     | 18       | E/PC0          | MC9            |

| 0x2_6000_0000            | 0x1_3000_0000           | Right     | 19       | E/PC1          | MC9            |

| 0x2_8000_0000            | 0x1_4000_0000           | Right     | 20       | B/PC0          | MC10           |

| 0x2_A000_0000            | 0x1_5000_0000           | Right     | 21       | B/PC1          | MC10           |

| 0x2_C000_0000            | 0x1_6000_0000           | Right     | 22       | F/PC0          | MC11           |

| 0x2_E000_0000            | 0x1_7000_0000           | Right     | 23       | F/PC1          | MC11           |

| 0x3_0000_0000            | 0x1_8000_0000           | Right     | 24       | C/PC0          | MC12           |

| 0x3_2000_0000            | 0x1_9000_0000           | Right     | 25       | C/PC1          | MC12           |

| 0x3_4000_0000            | 0x1_A000_0000           | Right     | 26       | G/PC0          | MC13           |

| 0x3_6000_0000            | 0x1_B000_0000           | Right     | 27       | G/PC1          | MC13           |

| 0x3_8000_0000            | 0x1_C000_0000           | Right     | 28       | D/PC0          | MC14           |

| 0x3_A000_0000            | 0x1_D000_0000           | Right     | 29       | D/PC1          | MC14           |

#### Table 6: AXI Port Assignments

| Start Address<br>(16 GB) | Start Address<br>(8 GB) | HBM Stack | AXI Port | HBM Channel/PC | HBM Controller |

|--------------------------|-------------------------|-----------|----------|----------------|----------------|

| 0x3_C000_0000            | 0x1_E000_0000           | Right     | 30       | H/PC0          | MC15           |

| 0x3_E000_0000            | 0x1_F000_0000           | Right     | 31       | H/PC1          | MC15           |

#### Table 6: AXI Port Assignments (cont'd)

*Note*: The AXI Start addresses mentioned in the table are hard coded regardless of how many stacks are enabled.

### **AXI Port Details**

For signal definitions and protocol, see the AMBA AXI Protocol Specification. When user parity is enabled, drive the correct parity value on WDATA\_PARITY for Write transactions. The RDATA\_PARITY bus provides the Read data parity along with the Read data. The parity calculation is done on a per-byte basis where a 1 is asserted if the sum of the bits in a byte is Odd.

Each AXI port can accept 64 read transactions and 32 write transactions.

### **Non-AXI Ports**

A single 32-bit APB register bus with 22 bits of addressing provides access to all the documented status registers for each HBM controller stack. For naming and protocol definitions, see the AMBA AXI Protocol Specification.

*Note*: apb\_slv\_error is not used.

There is one port per stack to indicate the end of initial configuration sequence through the internal APB master. This port is <code>apb\_complete\_0</code> for Stack-O APB interface and <code>apb\_complete\_1</code> for Stack-1 APB interface. You need to monitor these ports and wait until they sample high before starting any transaction on the AXI3 interface.

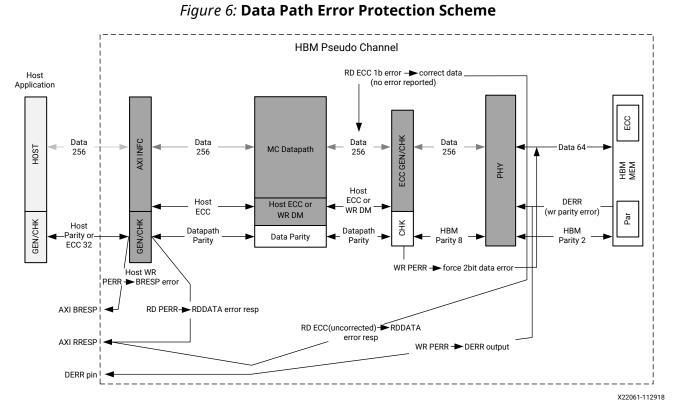

## **Data Path Error Protection**

- **BRESP error:** Occurs if host parity is enabled and a parity error is detected in the AXI port for any of the associated AXI Write data. An error drives 2'b10 on the BRESP port.

- **RRESP error:** Occurs if the corresponding read data has either a parity error or an uncorrectable ECC error. The parity error check covers the path from HBM memory to AXI RDATA output port. An error drives 2'b10 on the RRESP port.

*Note*: If parity retry is enabled, the error response will be asserted only if there is no read data transfer without parity errors.

- **DERR signal pulse:** Occurs if the HBM detects a parity error on Write data received. The DERR signal does not indicate exactly which AXI Write data command has caused the parity error.

- WDATA error insertion: Occurs if a Write data parity error is detected within the memory controller pipeline. Write data is corrupted to ensure that an ECC error will be detected at a later point when the data is read.

# Chapter 4

# Designing with the Core

This section includes guidelines and additional information to facilitate designing with the core.

# Clocking

There are three clock types that must be provided to the HBM core:

- The HBM\_REF\_CLK\_x drives a PLL which then generates a clock for the eight memory controllers, as well as the memory clock for the HBM stack. There is one PLL per HBM stack. This clock must be sourced from a MMCM/BUFG, or from a BUFG. The HBM\_REF\_CLK\_x can be sourced from the cascading clocking sources derived from another clock. The source clock for this derived clock must come from a GCIO pin within the same SLR as the HBM. The clock generator driving the GCIO should have jitter less than 3 pS RMS.

- The APB\_x\_PCLK is used for the APB register port access. This can be asynchronous to the other clocks. There is one APB clock port per HBM stack. The APB\_x\_PCLK can be sourced from the cascading clocking source or MMCM or GCIO pin.

- The AXI\_XX\_ACLK is the clock for each of the AXI ports. These can be asynchronous to the other clocks. The AXI\_XX\_ACLK can be sourced from the cascading clocking source or MMCM or GCIO pins.

The global routing switch does not have a separate clock input, but rather shares one of the  $AXI\_xx\_ACLKs$ . This is automatically selected by the software to be one of the clocks in the middle of the user-selected memory controllers. This can be checked by looking at the hbm\_0.v file. There are parameters,  $CLK\_SEL\_xx$ , and only one has the attribute TRUE.

For maximum efficiency, it is important that the AXI clock selected is the highest frequency of all of the AXI port clocks.

### AMD**Z** XILINX

# **HBM Performance Concepts**

The total performance of the HBM solution is dependent upon multiple factors:

- The HBM stack operating frequency

- The frequency of the AXI ports in the user application

- The HBM address map selection

- The global addressing mode

- The reordering options selected within the HBM IP

- The HBM stack temperature

The most important factor is how the user application logic is accessing the HBM through the AXI ports. System architects must consider how all these factors interact when evaluating the performance of the HBM memory solution in their design.

## **HBM Topology**

The Xilinx HBM solutions are available in either 4 GB or 8 GB per stack options, with nearly all configurations containing two stacks per FPGA. This means there is a total of 8 GB or 16 GB of available memory for these dual stack devices.

The total data-bit width of an HBM stack is 1024 bits divided across eight channels of 128 bits each. Each channel is serviced by a single memory controller which accesses the HBM in pseudo channel mode, meaning two semi-independent 64-bit data channels with a shared command/ address/control (CAC) bus. A 4 GB per stack device has 4 Gb per channel, and each channel has two 2 Gb or 256 MB pseudo channels. An 8 GB per stack device has 8 Gb per channel, and each channel has two 4 Gb or 512 MB pseudo channels.

Most of the HBM protocol requirements and timing can be evaluated on a pseudo channel basis, meaning that two Activate commands can be issued back to back to PCO and PC1 without considering tRRD. If two Activate commands are issued to the same pseudo channel back to back, tRRD must first expire before the second Activate command can be issued.

The HBM always operates with a burst length of 4 in pseudo channel mode. The HBM protocol closely matches that of DDR4 memory, so many of the same performance and protocol concepts apply. The clock rate of the HBM is set in the IP configuration options in the Vivado IDE. HBM is a double data rate (DDR) memory, so the data bus toggles at twice the interface clock rate.

## **Raw Throughput Evaluation**

It is important to understand the raw throughput of the HBM stacks and how the user logic must be designed to match this data rate. Each HBM stack has eight channels, each channel has a dedicated memory controller, each memory controller is operating in pseudo channel mode, each pseudo channel is 64 bits wide, and the data bits toggle at twice the HBM clock rate set in the IP configuration. If the HBM IP is configured with a 900 MHz clock rate, the toggle rate for a single HBM stack can be evaluated using the following formula:

(64 bits per pseudo channel) x (2 pseudo channels per memory controller) x (8 channels) x 900 MHz x 2

This results in 1,843,200 Mb per second per stack, or 230,400 MB per second per stack. Double this value to 460,800 MB per second for a dual stack device.

From the user logic perspective each AXI port for the HBM is 256 bits wide and there is one AXI port per pseudo channel in the stack. From the example above, the user logic must clock the AXI ports at 450 MHz to match the toggle rate of the HBM when it is running at 900 MHz. This is evaluated by the following formula:

(256 bits per AXI port) x (2 ports per memory controller) x (8 channels) x 450 MHz

This results in 1,843,200 Mb per second per stack, or 230,400 MB per second per stack. Double this value for 460,800 MB per second for a dual stack device with 32 AXI ports.

These are the raw HBM throughput calculations but as with all traditional volatile memories the arrays in the HBM stacks need to be refreshed to maintain data integrity. The base refresh interval (tREFI) for the HBM stacks is 3.9  $\mu$ s. For 4H devices, the refresh command period (tRFC) is 260 ns and for 8H devices it is 350 ns. Adding in the refresh overhead to the raw throughput of a 4H device causes the loss of approximately 7% of peak efficiency, and 8H devices lose approximately 9%. As is the case with traditional volatile memory, tREFI decreases as the temperature increases, so more available HBM interface time is lost to refresh overhead as the stacks heat up. The base rate of 3.9  $\mu$ s is used for temperatures from 0°C to 85°C. Between 85°C and 95°C tREFI is reduced to 1.95  $\mu$ s.

## **AXI Considerations**

The HBM IP requires a fixed AxSIZE of 0x5 for 32 bytes (256 bits) and it is recommended to have a minimum AxLEN of 0x1 to gain higher performance for linear accesses. Undersized AXI writes are supported by using the WSTRB port but these accesses decrease the total system performance. This is because the same amount of HBM protocol execution and interface time is used to service a full 32-byte Write as is used for an 8-byte Write. With this example the effective peak bandwidth is only 25% of the theoretical maximum.

### AMD**Z** XILINX

Another AXI consideration is to make sure that the AXI Write and Read addresses are aligned to the HBM physical address space and transaction size. The lower five bits of the AWADDAR and ARADDR should be unused to ensure that accesses align to the 32-byte HBM burst boundary. This is because each individual Write or Read transaction on the HBM interface is a burst length of 4 with a DQ bus width of 64 bits, resulting in a total of 32 bytes. The AXI address space is a byte address, so 32 bytes result in 5 bits of addressing, and these are placed at the bottom of the address space. If an AXI transaction has a non-zero value in these lower address bits, the HBM controller must execute multiple commands on the HBM interface. In the case of an unaligned Read operation, two Reads are required on the HBM interface to gather the data. The controller then coalesces this to the expected payload which is delivered to the AXI Read channel. Here, the effective bandwidth is 50% or less depending on the additional protocol churn on the HBM interface. The same situation can occur with an unaligned Write, where a single Write request executes as two writes on the HBM interface while using the data mask pins to mask the unused portion of the Write payload. If ECC is enabled, an unaligned Write executes as two Read/ Modify/Write (RMW) operations. When ECC is enabled the HBM controller cannot use the Data Mask pins so the first portion of the unaligned Write needs to be Read from the memory, then modified by the controller for a new data payload, and finally written back to the HBM. This process is executed twice because it requires two RMW operations to service the unaligned Write along the HBM burst boundaries.

The last AXI consideration is that the Write and Read channels operate independently while there is only a single electrical interface on the HBM stacks. This means that the HBM controller only executes Write operations and then must wait for the appropriate period of protocol time to service a bus turnaround before it can issue Read operations. For the highest possible efficiency, the user logic should minimize bus turnarounds, maximize the amount of time spent moving data in one direction before having to go the other way, or at least have a highly deterministic access pattern that minimizes protocol churn for simultaneous Write and Read streams.

### **HBM Address Map and Protocol Considerations**

To design the most efficient system architecture and user logic to access the HBM, it is important to understand the physical address space of the HBM as well as the address map option set in the IP configuration in the Vivado IDE. Understanding of these two aspects is required to evaluate the HBM protocol execution. This is the largest factor in evaluating a system performance based on the user logic AXI access pattern. The following table defines the HBM physical address map for 4H and 8H devices.

#### Table 7: Physical Address Map for 4H and 8H Devices

| HBM Arrangement            | 4H Device (4 GB per Stack)             | 8H Device (8 GB per Stack)             |

|----------------------------|----------------------------------------|----------------------------------------|

| Density per Channel        | 4 Gb                                   | 8 Gb                                   |

| Density per Pseudo Channel | 2 Gb                                   | 4 Gb                                   |

| Row Address                | RA[13:0]                               | RA[13:0]                               |

| Column Address             | CA[5:1]                                | CA[5:1]                                |

| Bank Group Address         | BA[3:0]                                | SID, BA[3:0]                           |

| Bank Arrangement           | 16 Banks<br>4 Bank Groups with 4 Banks | 32 Banks<br>8 Bank Groups with 4 Banks |

| Total User Address Bits    | 23                                     | 24                                     |

The total address space of a 4H device is 32 bits and for an 8H device it is 33 bits. The following table describes the AXI addressing for these devices.

#### Table 8: AXI Addressing for 4H and 8H Devices

| HBM Arrangement                  | 4H Device (4 GB per Stack) | 8H Device (8 GB per Stack) |

|----------------------------------|----------------------------|----------------------------|

| Total Address Bits               | 33 total as 32:0           | 34 total as 33:0           |

| Stack Select: 0 = Left 1 = Right | 32                         | 33                         |

| Destination AXI Port: 0 – 15     | 31:28                      | 32:29                      |

| HBM Address Bits                 | 27:5                       | 28:5                       |

| Unused Address Bits              | 4:0                        | 4:0                        |

HBM operation closely follows that of traditional volatile memories and is specifically similar to DDR4. The basics of protocol operation dictate the resulting efficiency when accessing the memory array, and this must be a significant consideration along with the user AXI access pattern and how the user logic is driving the AXI channels during operation.

Like DDR4, HBM uses the concept of Banks and Bank Groups for the memory and leveraging these concepts is how to achieve a highly efficient array access pattern. 4H devices have a total of 16 Banks, arranged as 4 Bank Groups each with 4 Banks. 8H devices have 32 Banks, arranged as 8 Bank Groups with 4 Banks.

The HBM supports one active Row address per Bank. Protocol access times between Banks in different Bank Groups are lower than when accessing Banks within the same Bank Group, and the currently active Row within a Bank must be Precharged before a different Row within that Bank can be activated. When a Row is activated within a Bank, it is recommended to perform multiple Column accesses within that Row before changing the Row. Doing this is considered to result in a high page hit rate, which means higher efficiency.

By default the HBM IP is set to a Row Bank Column addressing map with the Bank Group Interleave option enabled. With these default settings, the highest order address bits are the Row address (RAx) bits, of which only one Row address per Bank can be active at a time. The middle address bits are the Bank address bits, which are displayed as BGx for Bank Groups and BAx for Bank addresses. The next lowest address range is the Column address bits which are displayed as CAx, and these are accessed by Write and Read commands.

The Bank Group Interleave option means that BG0, the least significant bit of the Bank Group addressing, is placed as the least significant user address bit of the HBM memory map (addr[5]). With the default address map, an AXI transaction with an AxLEN of 0x1 and AxADDR of 0x0 executes two discrete commands on the HBM interface. The first goes to Row 0, Bank Group 0, Bank address 0, Column 0. The second goes to Row 0, Bank Group 1, Bank address 0, and Column 0.

Having the Bank Group Interleave option with BGO as the least significant bit is in service of sequential memory accesses. It decreases the amount of time spent waiting for protocol execution because the controller splits the accesses between two Banks in two separate Bank Groups. An AXI transaction with an AxLEN of 0x1 demonstrates this behavior, but fully leveraging these concepts for higher efficiency requires more consideration with longer transaction lengths or leveraging traffic streams mapped to Bank addresses across Bank Groups.

The default address map option is ideal for short mixed traffic because the Bank Group Interleave option alleviates some protocol exposure when the AxLEN is 0x1 or larger. This default address map option also supports the AXI reordering core which can help efficiency but might increase latency.

**IMPORTANT!** For 8H HBM devices the additional Bank bit is mapped to the SID bit, which is placed at the most significant address bit within the default Row Bank Column address map.

For 8H HBM devices the additional Bank bit is mapped to the SID bit which is placed at the most significant address bit with the default Row Bank Column address map. This is due to a limitation with the AXI Reordering core. Take notice with the default Row Bank Column address map and 8H devices to manage their traffic master addressing to use the SID bit as the most significant Bank Group bit. When a custom address map is used the SID bit can be placed as desired but the AXI Reordering Core is disabled.

When the Custom Address Map option is enabled in the HBM configuration in the Vivado IDE, more addressing options are available but the AXI Reordering Core is disabled. The Custom Address Map option makes it possible to manually assign address bits to other locations. The following sections discuss the concepts behind the Row Column Bank and Bank Row Column presets. While the presets might not be an ideal match for every application, it is still possible to manipulate any address bit to make it better suited for the use case. When the Custom Address Map option is enabled, the Bank Group Interleave setting goes to False, but once again it is possible to remap the BGO bit to the least significant bit position of the address space to achieve the same result.

**Note:** When the Custom Address Map option is enabled, many of the reordering options are no longer available. Efficiency and low latency must be achieved by having well-defined traffic masters and access patterns for the physical address map.

The Row Column Bank address map option is ideal for long sequential access patterns. This is because for long transaction lengths, for instance AxLEN of 0x8 or longer, the majority of the protocol exposure is hidden by Bank Group switching. This address map is best used when the AXI transactions are only going in one direction at a time. If the traffic must change direction, those accesses should target the same Row/Bank combinations to guarantee a page hit for the Column access. This means when a long sequence of Writes is being serviced, the user logic should not issue any Read requests because this causes a bus turnaround, resulting in idle periods on the HBM interface and lowering efficiency. If the Write and Read accesses do not target the same Row/Bank combinations, the user logic should never try to switch directions until the current access sequence is complete. In this scenario, if a Write stream is executing and a Read stream is trying to access a different Row/Bank combination, the controller issues multiple Precharge and Activate commands because the new traffic stream consists only of page misses. This causes a significant amount of idle time on the HBM interface and lowers efficiency.

The Bank Row Column address map option is ideal for designs where the user logic has segmented traffic streams into separate Bank Group and Bank address ranges. This means multiple traffic streams can operate independently in their own Bank Group/address combinations and use the remaining address space as required. In a simplified example scenario, there are two streams where one is mapped to BAO and BA1 across all Bank Groups while another is mapped to BA2 and BA3 across all Bank Groups. The first stream is long and sequential and the second stream is completely random and short. The first stream maintains high efficiency because it has a high page hit rate. The second stream with random addressing has low efficiency, but it never targets the same Bank/Row combination as the first stream, so high efficiency is maintained for the first stream. Without these considerations, if a traffic stream is long and sequential while another is random, the random stream interferes with the sequential stream and both have low efficiency.

### **HBM Reordering Options**