概述

Vitis 軟件平台開發環境

AMD Vitis™ 軟件平台是一款開發環境,主要用於開發包括 FPGA 架構、Arm® 處理器子係統和 AI 引擎在內的設計。Vitis 工具與 AMD Vivado™ ML Design Suite 相結合,可為設計開發提供更高層次的抽象。

Vitis 軟件平台包括以下工具:

- Vitis Embedded - 用於開發在嵌入式 Arm 處理器上運行的 C/C++ 應用代碼

- 編譯器和仿真器 - 用於使用 AI 引擎陣列實現設計

- Vitis HLS - 用於開發基於 C/C++ 的 IP 塊,該 IP 塊主要針對 FPGA 架構

- Vitis Model Composer 是一種基於模型的設計工具,可在 MathWorks Simulink® 環境中進行快速設計探索。

- 一係列性能優化的開源庫函數,如 DSP、視覺、求解器、超聲和 BLAS 等,其可采用 FPGA 架構實現,也可使用 AI 引擎實現

工具與庫

Vitis 嵌入式

Vitis™Embedded 是一個獨立的嵌入式軟件開發包,主要用於開發運行在嵌入式 Arm 處理器上的主機應用。

Vitis AIE DSP 設計工具

編譯器和仿真器

AMD Versal™ 自適應 SoC 器件具有 AI 引擎陣列,有助於采用資源和電源都優化的方式實現高性能 DSP 功能。將 AI 引擎與 FPGA 架構資源一起使用,有助於非常高效地實現高性能 DSP 應用。

了解如何使用 AMD Vitis 工具流程來為 DSP 應用釋放 AI 引擎的硬件加速功能。

Vitis HLS

Vitis HLS 工具允許用戶通過將 C/C++ 函數綜合成 RTL,輕鬆創建複雜的 FPGA 算法。

Vitis HLS 工具與 Vivado™ ML Design Suite(用於綜合、布局和布線)及 Vitis 統一軟件平台(用於異構係統設計和應用)高度整合。

Vitis Model Composer

Vitis Model Composer 是一款基於模型的設計工具,可在 MathWorks Simulink® 環境中實現快速的設計探索。

此外,該工具還允許您使用一係列 AI 引擎和可編程邏輯 (HDL/HLS) 塊對設計進行建模和仿真。

Vitis 庫

性能優化的開源庫,提供開箱即用的加速,對於采用 C、C++ 編寫的現有應用而言,代碼修改極少,甚至不需要修改代碼。

按原樣利用特定領域的加速庫,通過修改適應您的需求,或者在您的自定義加速器中用作算法構建塊。

工具使用

必須使用不同的 Vitis 工具來構建不同部分的 AMD 自適應 SoC 和 FPGA。

| FPGA(可編程邏輯) | 處理子係統 | AI 引擎 |

|---|---|---|

| Vivado Design Suite / Vitis HLS / Vitis Model Composer | Vitis 嵌入式 | AIE 編譯器和仿真器 / Vitis Model Composer |

設計流程

Vitis 嵌入式軟件開發流程

(習慣上稱為嵌入式 SDK,主要針對以前的 FPGA 係列)

從 Vivado 導出硬件,作為平台文件

開發應用代碼

調試並生成引導映像

在 AMD 自適應 SoC 中為 Arm® 嵌入式處理器子係統開發 C/C++ 代碼的設計人員通常會使用該流程。

- 硬件工程師不僅可設計可編程邏輯,而且還可使用 AMD Vivado™ ML Design Suite 將硬件按 Xilinx 支持存檔 (XSA) 文件導出。

- 軟件工程師可將這些硬件設計信息整合到他們的目標平台中,並可使用 Vitis 嵌入式軟件開發應用代碼。

開發人員可在 Vitis 嵌入式軟件中執行所有係統級驗證,並通過生成引導映像來啟動應用。

如欲了解使用 Vitis 軟件平台開發嵌入式軟件應用的工作流程,請參見《用戶指南 (UG1400)》中的“ Vitis 嵌入式軟件開發工具”章節。

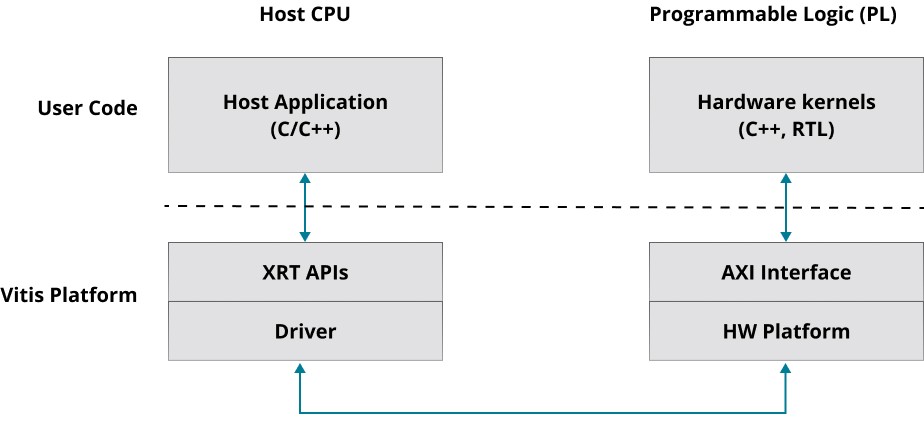

Vitis 係統設計流程

(硬件與軟件)

在 AMD 自適應 SoC 中集成其設計軟硬件部分的係統設計人員通常會使用該流程。

該流程用於開發異構嵌入式係統設計,其中包括運行在 Arm® 嵌入式處理器上的軟件應用,以及運行在可編程邏輯 (PL) 和 / 或 Versal™ AI 引擎陣列上的計算內核等。

該流程包括:

- 采用 C/C++ 編寫的軟件主機應用,通常運行在嵌入式 Arm 處理器子係統上。它使用 Xilinx 運行時庫 (XRT) 實現的原生 API 與 AMD 器件內的硬件內核交互。

- 硬件內核可使用 AMD Vitis™ HLS 工具從 C++ 生成,也可使用 AMD Vivado™ ML Design Suite 直接在 RTL 中描述。

如欲進一步了解使用 Vitis 統一軟件平台的異構係統設計流程,請參見《用戶指南 (UG1393)》中的“ Vitis 異構係統設計工具”章節。

AMD Alveo™ 數據中心加速卡采用相同的係統設計流程:軟件程序運行在 x86 主機上,內核運行在 PCIe® 連接的加速卡上的 FPGA 中。如欲進一步了解使用 Vitis 統一軟件平台的數據中心加速流程,請參見《用戶指南 (UG1393)》中的“ Vitis 數據中心加速工具”章節。

下載

訪問下載頁麵,以訪問全新 AMD Vitis™ 統一軟件平台。

新增功能

2024.1 的新特性

AMD Versal™ AI 引擎 DSP 設計的增強功能

- AI 引擎 AIE 和 AIE-ML 的最新增強型 DSP 及 Solver 庫函數

- AI 引擎仿真器的易用特性

麵向 AMD Vitis™ 統一軟件平台的重要提升功能

- 新器件支持:AMD Versal™ Premium VP1902 自適應 SoC、AMD MicroBlaze™ V 處理器

- 針對 Windows® 環境增強了嵌入式應用開發與 BSP 生成

- 用戶管理流程,調試外部編譯的嵌入式應用

- 最新 Bootgen GUI

- 為平台項目啟用增量構建

AMD Vitis IDE 的重大改進(全新 GUI)

- 支持處理子係統層級調試

- 支持項目/工作區的導出與導入

- 支持 Python 解釋器及 API

- 新特性預覽頁麵

- 嵌入式、AI 引擎及平台項目的新文件修改通知

如需了解更多詳情,請訪問我們的新现金网博e百 頁麵。